# Vivado Design Suite User Guide

# **Using Tcl Scripting**

UG894 (v2017.1) April 5, 2017

## **Revision History**

The following table shows the revision history for this document.

| Date      | Version | Revision                                                                                                                            |

|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| 4/05/2017 | 2017.1  | Updated screen displays throughout the manual to reflect the latest (2017.1) versions of the Vivado Design Suite and Tcl Store GUI. |

|           |         | Updated Calling External Programs section to include an example for Windows.                                                        |

|           |         | Added information to the section Initializing Tcl Scripts.                                                                          |

|           |         | Updated the name of the Vivado Design Suite startup script to Vivado_init.tcl.                                                      |

## **Table of Contents**

| Revision History                             |

|----------------------------------------------|

| Introduction                                 |

| A Brief Overview of Tcl                      |

| Getting Help                                 |

| Platform Specific Tcl Behaviors 10           |

| Compilation and Reporting Example Scripts 10 |

| Loading and Running Tcl Scripts 18           |

| Writing a Tcl Script                         |

| Accessing Design Objects                     |

| Handling Lists of Objects                    |

| Redirecting Output                           |

| Controlling Loops                            |

| Error Handling                               |

| Accessing Environment Variables              |

| Calling External Programs                    |

| Vivado GUI/Tcl Modes Versus Batch Mode       |

| Creating Custom Design Rules Checks (DRCs)   |

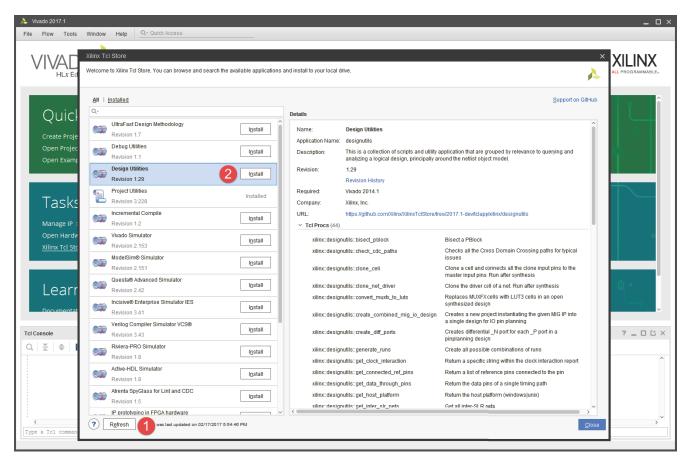

| Xilinx Tcl Store         70                  |

| Tcl Scripting Tips                           |

#### Appendix A: Additional Resources and Legal Notices

| Xilinx Resources                        | 102 |

|-----------------------------------------|-----|

| Solution Centers                        | 102 |

| Documentation Navigator and Design Hubs | 102 |

| References                              | 103 |

| Training Resources                      | 103 |

| Please Read: Important Legal Notices    | 104 |

## Tcl Scripting in Vivado

### Introduction

The Tool Command Language, or Tcl, is an interpreted programming language with variables, procedures, and control structures, to interface to a variety of design tools and to the design data.

**TIP:** For more information, see the Vivado Design Suite Tcl Command Reference Guide (UG835) [Ref 1], or type < command> -help. For information on launching and using the Vivado® Design Suite, see the Vivado Design Suite User Guide: Getting Started (UG910) [Ref 2].

The language is easily extended with new function calls, so that it has been expanded to support new tools and technology since its inception and adoption in the early 1990s. It has been adopted as the standard application programming interface, or API, among most EDA vendors to control and extend their applications.

Xilinx® has adopted Tcl as the native programming language for the Vivado Design Suite, as it is easily adopted and mastered by designers familiar with this industry standard language. The Tcl interpreter inside the Vivado Design Suite provides the full power and flexibility of the Tcl language to control the application, access design objects and their properties, and create custom reports. Using Tcl, you can adapt your design flow to meet specific design challenges.

The Tcl language provides built-in commands to read and write files to the local file system. This enables you to dynamically create directories, start FPGA design projects, add files to the projects, run synthesis and implementation. You can customize the reports generated from design projects, on device utilization and quality of results, to share across the organization.

You can also use the Tcl language to implement new design approaches, or work around existing problems, inserting and deleting design objects, or modifying properties as needed. You can write scripts to replay established portions of your design flow to standardize the process.

Many of the Tcl commands discussed in the following text and script examples are specific to the Vivado Design Suite. You can find detailed information regarding Vivado specific Tcl commands in the *Vivado Design Suite Tcl Command Reference Guide* (UG835) [Ref 1], or in the Help system of the Vivado tools.

The Vivado IDE uses Xilinx Design Constraints (XDC) to specify the design constraints. XDC is based on a subset of all the Tcl commands available in Vivado and is interpreted exactly like Tcl. The XDC commands are primarily timing constraints, physical constraints, object queries and a few Tcl built-in commands: set, list, and expr. For a complete description of the XDC commands, see Appendix B of the *Vivado Design Suite User Guide: Using Constraints* (UG903) [Ref 3]. Unlike Tcl scripts, XDC files are managed by the Vivado IDE so that any constraint edited through the graphical interface or the Timing Constraints Editor can be saved back to its original XDC file. For this reason, only XDC commands can be used in a XDC file. If you need to use other Tcl commands to write your constraints, you must use a Tcl script.

The Vivado tools write a journal file called vivado.jou into the directory from which Vivado was launched. The journal is a record of the Tcl commands run during the session that can be used as a starting point to create new Tcl scripts.

A log file, vivado.log is also created by the tool and includes the output of the commands that are executed. Both the journal and log file are useful to verify which commands were run and what result they produced.

Additional Tcl commands are provided by the Tcl interpreter that is built into the Vivado Design Suite. For Tcl built-in commands, Tcl reference material is provided by the Tcl Developer Xchange website, which maintains the open source code base and documentation for Tcl, and is located at <u>http://www.tcl.tk</u>.

See <u>http://www.tcl.tk/man/tcl8.5/tutorial/tcltutorial.html</u> [Ref 8] for an introductory tutorial to the Tcl programming language. Also see the Tclers Wiki located at <u>http://wiki.tcl.tk</u> for some example scripts.

In this document you will see some examples of Tcl commands and Tcl scripts, and the results that are returned by the Vivado Design Suite when these commands are run. The commands and their return values appear with the following formats:

• Tcl commands and example scripts:

puts \$outputDir

• Output to Tcl Console or results of Tcl commands:

./Tutorial\_Created\_Data/cpu\_output

## A Brief Overview of Tcl

A Tcl script is a series of Tcl commands, separated by new-lines or semicolons. A Tcl command is a string of words, separated by blanks or tabs. The Tcl interpreter breaks the command line into words and performs command and variable substitutions as needed. The Tcl interpreter reads the line from left to right, evaluates each word completely before attempting to evaluate the next. Command and variable substitutions are performed from left to right as the line is read.

A word is a string that can be a single word, or multiple words within braces, {}, or multiple words within quotation marks, "". Semicolons, brackets, tabs, spaces, and new-lines, within quotation marks or braces are treated as ordinary characters. However, the backslash, \, is treated as a special character even within braces and quotation marks, as discussed below.

The first word identifies the command, and all subsequent words are passed to the command as arguments.

```

set outputDir ./Tutorial_Created_Data/cpu_output

```

In the preceding example, the first word is the Tcl set command, which is used to assign variables. The second and third words are passed to the set command as the variable name (outputDir), and the variable value (./Tutorial\_Created\_Data/cpu\_output).

When a backslash, '\', is used in a word, then the Tcl interpreter performs backslash substitution. In most cases, this means that the character following the backslash is treated as a standard character in the word. This is used to add quotes, braces, dollar signs, or other special characters to a string. Refer to a Tcl/Tk reference source for more information on how the Tcl interpreter handles the backslash character.

```

puts $outputDir

./Tutorial_Created_Data/cpu_output

puts \$outputDir

$outputDir

```

There is a also difference between the use of braces and quotation marks. No substitutions are performed on the characters between the braces. Words, or strings, within braces are taken verbatim, and are not evaluated for variable or command substitution by the Tcl interpreter. The word consists of exactly the characters between the outer braces, not including the braces themselves, as shown in the example below. Strings within quotation marks are evaluated, and variable and command substitutions are performed as needed. Command substitution, variable substitution, and backslash substitution are performed on the characters between quotes.

```

puts {The version of Vivado Design Suite is [version -short]}

The version of Vivado Design Suite is [version -short]

puts "The version of Vivado Design Suite is [version -short]"

The version of Vivado Design Suite is 2016.1

```

Notice in the example above, that the [version -short] command is substituted for the returned value when enclosed within quotation marks, but is not substituted when enclosed within braces. Keep substitution in mind when choosing to use either "" or {} to enclose a string of words.

Variable assignment is performed using the set command. You can access a previously assigned variable by specifying the name of the variable with a leading dollar sign, '\$'. If a word starts with a dollar sign the Tcl interpreter performs variable substitution, replacing the variable with the value currently stored by the variable. The '\$' is a reserved character in the Tcl language.

```

set outputDir ./Tutorial_Created_Data/cpu_output

puts $outputDir

./Tutorial_Created_Data/cpu_output

```

Commands can also be nested inside other commands within brackets, [], which are evaluated from left to right in a bottom-up manner. The Tcl interpreter recursively processes the strings within the brackets as a new Tcl script. A nested command can also contain other nested commands. The result of a nested command is passed up into the higher-level command, which is then processed.

```

set listCells [lsort [get_cells]]

```

The preceding example assigns the sorted list of cell objects existing at the top-level of the current design to the listCells variable. The get\_cells command is executed first, the returned objects are sorted by the lsort command, and the sorted list is assigned to the specified variable.

However, the Vivado Design Suite handles square brackets slightly differently than standard Tcl. Square brackets are treated as standard characters in Verilog and VHDL names (net, instances, etc.), and usually identify one or more elements of vectors, such as busses or arrays of instances. In the Vivado tools the square brackets are not evaluated in a bottom-up manner when they are expected to be part of a netlist object name.

The following three commands are equivalent:

```

1.) set list_of_pins [get_pins transformLoop[0].ct/xOutReg_reg/CARRYOUT[*] ]

2.) set list_of_pins [get_pins {transformLoop[0].ct/xOutReg_reg/CARRYOUT[*] } ]

3.) set list_of_pins [get_pins transformLoop\[0\].ct/xOutReg_reg/CARRYOUT\[*\] ]

```

In line 1, the outer pair of brackets indicate a nested command, [get\_pins], as is standard in Tcl. However, the subsequent square brackets are interpreted by the Vivado tools as part of the specified object name transformLoop[0]. This is handled automatically by the Vivado Design Suite, but is limited to certain characters. These characters must be in one of the following forms, or the brackets will be interpreted as they would be in normal Tcl syntax:

- star: [\*] The wildcard indicates any of a number of bits or instances.

- integer: [12] The integer indicates a specific bit or instance.

In line 2 the use of the braces, {}, will prevent command substitution of the string inside the braces. In this case the square brackets would be evaluated as part of the object name, transformLoop[0].

In line 3, the backslash indicates that the bracket should be interpreted as a standard character rather than a special character, and this will prevent nested command substitution.

While lines 2 and 3 prevent the square brackets from being misinterpreted, those lines require you to manually apply the braces or backslash as needed by standard Tcl. Line 1 shows how the Vivado Design Suite automatically handles this for you.

Finally, to add comments to a Tcl script, simply start a new-line with the number sign, or hash character, '#'. Characters that follow a hash character are ignored, up to the next new-line. To add a comment to the end of a line, simply end the command with a semicolon, ';', and then begin the comment with a hash character as shown below:

```

# This is a comment

puts "This is a command"; # followed by a comment

```

## **Getting Help**

You can get help directly from the Tcl console. Every Vivado command supports the -help command line argument that can be used anywhere in the line.

For example:

```

Vivado% create_clock -help

Vivado% create_clock -name CLK1 -period 10 -help

```

In addition, there is a help command that provides additional information. Providing a command name to the help command (that is, help <*command*>) reports the same help information as <*command*> -help:

```

Vivado% help create_clock

```

The help command can also just return a short description of the arguments with the -args option:

```

Vivado% help create_clock -args

create_clock

Description:

Create a clock object

Syntax:

create_clock -period <arg> [-name <arg>] [-waveform <args>] [-add] [-quiet]

[-verbose] [<objects>]

Returns:

new clock object

Usage:

Name

Description

_____

-period Clock period: Value > 0

[-name] Clock name

[-waveform] Clock edge specification

[-add] Add to the existing clock in source_objects

[-quiet] Ignore command errors

[-verbose] Suspend message limits during command execution

[<objects>] List of clock source ports, pins or nets

```

A short summary of the syntax of a command is also available with the -syntax option:

```

Vivado% help create_clock -syntax

create_clock

Syntax:

create_clock -period <arg> [-name <arg>] [-waveform <args>] [-add]

[-quiet][-verbose] [<objects>]

```

In addition to providing help for the specific commands, the help command can also provide information on categories of commands or classes of objects. A list of categories can be obtained by executing the help command without any argument or option. A non-exhaustive list of categories is:

```

Vivado% help

ChipScope

DRC

FileIO

Floorplan

GUIControl

IPFlow

Object

PinPlanning

Power

Project

PropertyAndParameter

Report

SDC

Simulation

TclBuiltIn

```

Timing ToolLaunch Tools XDC

The list of commands available under each category can be also reported with the -category option. For example, the following command reports all the commands under the Tools category:

| Vivado% help -category tools           |                                           |                                                                                                                                                                                                                                           |  |  |

|----------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Topic                                  |                                           | Description                                                                                                                                                                                                                               |  |  |

| link_(                                 | design                                    | Open a netlist design                                                                                                                                                                                                                     |  |  |

| list_:                                 | features                                  | List available features.                                                                                                                                                                                                                  |  |  |

| load_:                                 | features                                  | Load Tcl commands for a specified feature.                                                                                                                                                                                                |  |  |

| opt_de                                 | esign                                     | Optimize the current netlist. This will perform the retarget, propconst, and sweep optimizations by default.                                                                                                                              |  |  |

| phys_(                                 | opt_design                                | Optimize the current placed netlist.                                                                                                                                                                                                      |  |  |

| place                                  | _design                                   | Automatically place ports and leaf-level instances                                                                                                                                                                                        |  |  |

| route                                  | _design                                   | Route the current design                                                                                                                                                                                                                  |  |  |

| synth                                  | _design                                   | Synthesize a design using Vivado Synthesis and open that design                                                                                                                                                                           |  |  |

| <br>opt_de<br>phys_c<br>place<br>route | esign<br>opt_design<br>_design<br>_design | Optimize the current netlist. This will perform the retarget,<br>propconst, and sweep optimizations by default.<br>Optimize the current placed netlist.<br>Automatically place ports and leaf-level instances<br>Route the current design |  |  |

## **Platform Specific Tcl Behaviors**

In some rare cases, Tcl can behave differently depending on the platform where it is being used (32 bit or 64 bit). This is not related to Vivado but to Tcl.

For example, if you have a list of large integers that you want to sort, you might use the following command:

```

vivado% lsort $list -integer

```

The command above does not behave the same whether the script is running on a 32-bit or 64-bit machine. The reason is that integers are coded differently on a 32-bit platform versus 64-bit platform:

```

win32, win64, lnx32: sizeof(int) is 4bytes

lnx64: sizeof(int) is 8bytes

```

A workaround for that particular example would be to use the command line option -command of lsort and provide a custom proc to do the sorting.

## **Compilation and Reporting Example Scripts**

#### **Compilation with a Non-Project Flow**

The following is an example Tcl script that defines a Non-Project design flow.

www.xilinx.com

The example script uses a custom command reportCriticalPaths. This is an illustration on how the Vivado Design Suite can be augmented with custom commands and procedures. The content of reportCriticalPaths is provided and explained in the section Defining Tcl Procedures.

```

# STEP#1: define the output directory area.

#

set outputDir ./Tutorial_Created_Data/cpu_output

file mkdir $outputDir

#

# STEP#2: setup design sources and constraints

#

read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ]

read_vhdl ./Sources/hdl/bft.vhdl

read_verilog [ glob ./Sources/hdl/*.v ]

read_verilog [ glob ./Sources/hdl/mgt/*.v ]

read_verilog [ glob ./Sources/hdl/or1200/*.v ]

read_verilog [ glob ./Sources/hdl/usbf/*.v ]

read_verilog [ glob ./Sources/hdl/wb_conmax/*.v ]

read_xdc ./Sources/top_full.xdc

#

# STEP#3: run synthesis, write design checkpoint, report timing,

# and utilization estimates

#

synth_design -top top -part xc7k70tfbg676-2

write_checkpoint -force $outputDir/post_synth.dcp

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_utilization -file $outputDir/post_synth_util.rpt

#

# Run custom script to report critical timing paths

reportCriticalPaths $outputDir/post_synth_critpath_report.csv

#

# STEP#4: run logic optimization, placement and physical logic optimization,

# write design checkpoint, report utilization and timing estimates

#

opt_design

reportCriticalPaths $outputDir/post_opt_critpath_report.csv

place_design

report_clock_utilization -file $outputDir/clock_util.rpt

#

# Optionally run optimization if there are timing violations after placement

if {[get_property SLACK [get_timing_paths -max_paths 1 -nworst 1 -setup]] < 0} {

puts "Found setup timing violations => running physical optimization"

phys_opt_design

}

write_checkpoint -force $outputDir/post_place.dcp

report_utilization -file $outputDir/post_place_util.rpt

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

#

# STEP#5: run the router, write the post-route design checkpoint, report the routing

# status, report timing, power, and DRC, and finally save the Verilog netlist.

route_design

write_checkpoint -force $outputDir/post_route.dcp

report_route_status -file $outputDir/post_route_status.rpt

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

```

www.xilinx.com

11

```

write_verilog -force $outputDir/cpu_impl_netlist.v -mode timesim -sdf_anno true

#

# STEP#6: generate a bitstream

#

write_bitstream -force $outputDir/cpu.bit

```

#### Details of the Sample Script

The key steps of the preceding script can be broken down as follows:

- **Step 1:** Defines a variable, <code>\$outputDir</code>, that points to an output directory and also physically creates the directory. The <code>\$outputDir</code> variable is referenced as needed at other points in the script.

- **Step 2:** Reads the VHDL and Verilog files that contain the design description, and the XDC file that contains the physical and/or timing constraints for the design. You can also read synthesized netlists (EDIF or NGC) using the read\_edif command.

The Vivado Design Suite uses design constraints to define requirements for both the physical and timing characteristics of the design. The read\_xdc command reads an XDC constraints file which will be used during synthesis and implementation.

**IMPORTANT:** The Vivado Design Suite does not support the UCF format. For information on migrating UCF constraints to XDC commands refer to the ISE to Vivado Design Suite Migration Guide (UG911) [Ref 4] for more information.

The read\_\* Tcl commands are designed for use with the Non-Project Mode, as it allows a file on the disk to be read by the Vivado Design Suite to build an in-memory design database, without copying the file or creating a dependency on the file in any way, as it would in Project Mode. All actions taken in the Non-Project Mode are directed at the in-memory database within the Vivado tools. The advantages of this approach make the Non-Project Mode extremely flexible with regard to the design. However, a limitation of the Non-Project Mode is that you must monitor any changes to the source design files, and update the design as needed. For more information on running the Vivado Design Suite using either Project Mode or Non-Project Mode, refer to the Vivado Design Suite User Guide: Design Flows Overview (UG892) [Ref 5].

**Step 3:** Synthesizes the design on the specified target device.

This step compiles the HDL design files, applies the timing constraints located in the XDC file, and maps the logic onto Xilinx primitives to create a design database in memory. The in-memory design resides in the Vivado tools, whether running in batch mode, Tcl shell mode for interactive Tcl commands, or in the Vivado Integrated Design Environment (IDE) for interaction with the design data in a graphical form.

Once synthesis completes, a checkpoint is saved for reference. At this point the design is an unplaced synthesized netlist with timing and physical constraints. Various reports

like timing and utilization can provide a useful resource to better understand the challenges of the design.

This sample script uses a custom command, reportCriticalPaths, to report the TNS/WNS/Violators into a CSV file. This provides the ability for you to quickly identify which paths are critical.

Any additional XDC file read in after synthesis by the read\_xdc or source commands is used during the implementation steps only. They will be stored in any subsequent design checkpoints, along with the netlist.

**Step 4:** Performs pre-placement logic optimization, in preparation for placement and routing. The objective of optimization is to simplify the logic design before committing to physical resources on the target part. Optimization is followed by timing-driven placement with the Vivado placer.

After each of those steps, the reportCriticalPaths command is run to generate a new CSV file. Having multiple CSV files from different stages of the design lets you create a custom timing summary spreadsheet that can help visualizing how timing improves during each implementation step.

Once the placement is done, the script uses the get\_timing\_paths command to examine the SLACK property of the worst timing path in the placed design. While the report\_timing command returns a detailed text report of the timing path with the worst slack, the get\_timing\_paths command returns the same timing path as a Tcl object with properties that correspond to the main timing characteristics of the path. The SLACK property returns the slack of the specified timing path, or worst path in this case. If the slack is negative then the script runs physical optimization to resolve the placement timing violations whenever possible.

At the very end of Step 4, another checkpoint is saved and the device utilization is reported along with a timing summary of the design. This will let you compare pre-routed and post-routed timing to assess the impact that routing has on the design timing.

- **Step 5:** The Vivado router performs timing-driven routing, and a checkpoint is saved for reference. Now that the in-memory design is routed, additional reports provide critical information regarding power consumption, design rule violations, and final timing. You can output reports to files, for later review, or you can direct the reports to the Vivado IDE for more interactive examination. A Verilog netlist is exported, for use in timing simulation.

- Step 6: Writes a bitstream to test and program the design onto the Xilinx FPGA.

#### **Compilation with a Project Flow**

The following script illustrates a Project flow that synthesizes the design and performs a complete implementation, including bitstream generation. It is based on the CPU example design provided in the Vivado installation tree.

```

#

# STEP#1: define the output directory area.

#

set outputDir ./Tutorial_Created_Data/cpu_project

file mkdir $outputDir

create_project project_cpu_project ./Tutorial_Created_Data/cpu_project \

-part xc7k70tfbg676-2 -force

#

# STEP#2: setup design sources and constraints

add_files -fileset sim_1 ./Sources/hdl/cpu_tb.v

add_files [ glob ./Sources/hdl/bftLib/*.vhdl ]

add_files ./Sources/hdl/bft.vhdl

add_files [ glob ./Sources/hdl/*.v ]

add_files [ glob ./Sources/hdl/mgt/*.v ]

add_files [ glob ./Sources/hdl/or1200/*.v ]

add_files [ glob ./Sources/hdl/usbf/*.v ]

add_files [ glob ./Sources/hdl/wb_conmax/*.v ]

add files -fileset constrs 1 ./Sources/top full.xdc

set_property library bftLib [ get_files [ glob ./Sources/hdl/bftLib/*.vhdl ]]

# Physically import the files under project_cpu.srcs/sources_1/imports directory

import_files -force -norecurse

#

# Physically import bft_full.xdc under project_cpu.srcs/constrs_1/imports directory

import_files -fileset constrs_1 -force -norecurse ./Sources/top_full.xdc

# Update compile order for the fileset 'sources_1'

set_property top top [current_fileset]

update_compile_order -fileset sources_1

update_compile_order -fileset sim_1

#

# STEP#3: run synthesis and the default utilization report.

#

launch_runs synth_1

wait_on_run synth_1

# STEP#4: run logic optimization, placement, physical logic optimization, route and

#

bitstream generation. Generates design checkpoints, utilization and timing

#

reports, plus custom reports.

set_property STEPS.PHYS_OPT_DESIGN.IS_ENABLED true [get_runs impl_1]

set_property STEPS.OPT_DESIGN.TCL.PRE [pwd]/pre_opt_design.tcl [get_runs impl_1]

set_property STEPS.OPT_DESIGN.TCL.POST [pwd]/post_opt_design.tcl [get_runs impl_1]

set_property STEPS.PLACE_DESIGN.TCL.POST [pwd]/post_place_design.tcl [get_runs impl_1]

set_property STEPS.PHYS_OPT_DESIGN.TCL.POST [pwd]/post_phys_opt_design.tcl [get_runs impl_1]

set_property STEPS.ROUTE_DESIGN.TCL.POST [pwd]/post_route_design.tcl [get_runs impl_1]

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

puts "Implementation done!"

```

#### Details of the Sample Script

• **Step 1:** The project is created with the create\_project command. The project directory and the target device are specified. The project directory is automatically created if it does not already exist.

In this example, the output directory where the various reports are saved is the same as the project directory.

• Step 2: All the files that are used in a project need to be explicitly declared and added to the project. This is done with the add\_files command. When a file is added to the project, it is added to a specific fileset. A fileset is a container that groups files together for a purpose. In this example script, most of the files are added to the default fileset (sources\_1). Only the Verilog testbench cpu\_tb.v is added to the default simulation fileset sim\_1.

The files are also copied inside the project directories with the import\_files command. By doing this, the project points to the local copy of the source files and does not track the original source files anymore.

• **Step 3:** The design is synthesized by launching a synthesis run in the background (launch\_run synth\_1). The Vivado IDE automatically generates all the necessary scripts to run synthesis in a separate Vivado session. Because synthesis runs in a different process, it is necessary to wait for its completion before continuing the current script. This is done by using the wait\_on\_run command.

Once the synthesis run is completed, the results can be loaded in memory with the open\_run synth\_1 command. A checkpoint without constraints is saved in the project directories, where synthesis was run. In this example, it can be found under:

./Tutorial\_Created\_Data/cpu\_project/project\_cpu.runs/synth\_1/top.dcp

**Note:** The names synth\_1 and impl\_1 are default names for the synthesis and implementation runs. Additional runs can be created with create\_run command.

• **Step 4:** The implementation is done by using the launch\_run command. The complete P&R flow from pre-place optimization to writing the bitstream can be performed in a single command. In this example script, the implementation is done up to the bitstream generation (launch\_run impl\_1 -to\_step write\_bitstream).

The optional step phys\_opt\_design is enabled in the script through the property STEPS.PHYS\_OPT\_DESIGN.IS\_ENABLED. Unlike with the non-project flow which allows dynamically calling the implementation commands based on conditions defined by the user, the run of a project flow must be configured statically before it is launched. This is why, in this example, the physical logic optimization step is enabled without checking the timing slack value after placement, unlike in the Compilation with a Non-Project Flow example.

The various reports are generated before or after each implementation step by using the run Tcl hook properties STEPS.<STEPNAME>.TCL.PRE and

STEPS. < STEPNAME>. TCL. POST. These properties allow the user to specify where a Tcl script is executed in the flow when using the run infrastructure. See Defining Tcl Hook Scripts for additional information.

Because the implementation run is executed in a separate Vivado session, all the Tcl variables and procs need to be initialized in that session in order to be used by the scripts. This can be done in several ways:

- **Method 1:** Define the Tcl variables and procs in your Vivado\_init.tcl (see Initializing Tcl Scripts). This is sticky to all your Vivado projects and sessions.

- **Method 2:** Add a Tcl script which contains the variables and procs to the constraints set used by the run. It will always be sourced as part of your constraints when opening the design in memory.

- Method 3: Set STEPS.OPT\_DESIGN.TCL.PRE to a Tcl script which contains the variables and proc. This script will only be sourced if the OPT\_DESIGN step is enabled, which is true by default.

The current example uses the Method 3. The Tcl scripts are associated with the implementation steps as follow:

| set_property | STEPS.OPT_DESIGN.TCL.PRE       | [pwd]/pre_opt_design.tcl       | [get_runs | impl_1] |

|--------------|--------------------------------|--------------------------------|-----------|---------|

| set_property | STEPS.OPT_DESIGN.TCL.POST      | [pwd]/post_opt_design.tcl      | [get_runs | impl_1] |

| set_property | STEPS.PLACE_DESIGN.TCL.POST    | [pwd]/post_place_design.tcl    | [get_runs | impl_1] |

| set_property | STEPS.PHYS_OPT_DESIGN.TCL.POST | [pwd]/post_phys_opt_design.tcl | [get_runs | impl_1] |

| set_property | STEPS.ROUTE_DESIGN.TCL.POST    | [pwd]/post_route_design.tcl    | [get_runs | impl_1] |

The absolute Tcl script path must be specified because the implementation run is executed in a sub-directory of the project tree, which is different from the one where the full compilation Tcl script is executed.

• pre\_opt\_design.tcl

The two first lines correspond to the initialization of the variable and proc used by several scripts later in the implementation run. The three next lines run some utilization and timing reports. It is generally recommended to run timing analysis at the beginning of implementation to validate the timing constraints used during place and route, and insure there is no large violation. The reportCriticalPaths report provides more info on the worst paths of the design. This Tcl proc is described further in Defining Tcl Procedures.

post\_opt\_design.tcl

This script does not need to define the outputDir variable and reportCriticalPaths proc because they are already defined in pre\_opt\_design.tcl which is sourced earlier in the run in the same Vivado session.

It is recommended to also run utilization and timing analysis after opt\_design.

• post\_place\_design.tcl

After placement, you can review the utilization of the clock resources and where they are located in the device. It is recommended to run timing analysis to identify large timing violations that cannot be resolved later in the flow.

post\_phys\_opt\_design.tcl

Like after placement, it is important to review the timing report at this point of the flow.

post\_route\_design.tcl

After route, the timing analysis uses actual routed net delays and must be reviewed for timing sign-off. The route status report summarizes the number of unresolved routing issues. If there are any, the DRC report often helps identify what the routing issues are.

**Note:** When running an implementation step inside the hook script, you can use the Tcl variable ACTIVE\_STEP to, for instance, make the report file names unique. The variable ACTIVE\_STEP is automatically updated by Vivado when using the run infrastructure. See Sharing Hook Scripts Between Steps for more information.

**Note:** Most of the Tcl reports generated during post-route above are also automatically created by the run infrastructure. Similarly, a design checkpoint is generated after each step of the flow, so there is usually no need to call the write\_checkpoint command in your scripts when using a project flow. You can find all the checkpoints and default reports in the implementation run directory:

```

./Tutorial_Created_Data/cpu_project/project_cpu.runs/impl_1/

top_opt.dcp

top_placed.dcp

top_routed.dcp

top_clock_utilization_placed.rpt

top_control_sets_placed.rpt

top_utilization_placed.rpt

top_loced.rpt

top_drc_routed.rpt

top_ower_routed.rpt

top_route_status.rpt

top_timing_summary_routed.rpt

```

After the implementation run is complete, the implemented design can be loaded in memory with the open\_run impl\_1 command.

## Loading and Running Tcl Scripts

The Vivado Design Suite offers several different ways to load and run a Tcl script during a design session. You can have script files loaded automatically when the tool is launched, source scripts from the Tcl command line, or add them to the menus in the Vivado IDE.

#### **Initializing Tcl Scripts**

The Vivado Design Suite can automatically load Tcl scripts defined in Vivado\_init.tcl file. This approach is useful when you have written Tcl procedures that define new commands that you want to make available in all your Vivado sessions.

**Note:** Starting with 2017.1 the startup script for the Vivado Design Suite has been renamed Vivado\_init.tcl. In the earlier versions it was called init.tcl. If Vivado\_init.tcl does not exist but init.tcl is present, the Vivado tools source the init.tcl and issue a deprecation message.

When you start the Vivado tools, it looks for a Tcl initialization script in several locations with the following precedence:

1. In the software installation:

<installdir>/Vivado/version/scripts/Vivado\_init.tcl

Where *<installdir>* is the installation directory where the Vivado Design Suite is installed.

- 2. In the local user directory (Vivado tools version dependent):

- a. For Windows 7: %APPDATA%/Xilinx/Vivado/<VivadoVersion>/Vivado\_init.tcl

For example: %APPDATA%/Xilinx/Vivado/2017.1/Vivado\_init.tcl

b. For Linux: \$HOME/.Xilinx/Vivado/<VivadoVersion>/Vivado\_init.tcl

For example: \$HOME/.Xilinx/Vivado/2017.1/Vivado\_init.tcl

- 3. In the local user directory (Vivado tools version independent):

- a. For Windows 7: %APPDATA%/Xilinx/Vivado/Vivado\_init.tcl

- b. For Linux: \$HOME/.Xilinx/Vivado/Vivado\_init.tcl

If Vivado\_init.tcl exists in several locations, the Vivado tool sources the file following the precedence explained above.

The Vivado\_init.tcl file in the installation directory allows a company or design group to support a common initialization script for all users. Anyone starting the Vivado tools from that software installation sources the enterprise Vivado\_init.tcl script.

The Vivado\_init.tcl file in the home directory allows each user to specify additional commands, or to override commands from the software installation to meet their specific design requirements.

The Vivado\_init.tcl file is a standard Tcl script file that can contain any valid Tcl command supported by the Vivado tools. You can even source another Tcl script file from within Vivado\_init.tcl by adding the source command.

**Note:** Vivado\_init.tcl follows the naming convention <program>\_init.tcl. Other supported program names are xsim and vivado\_lab. For instance, XSim looks for xsim\_init.tcl at startup.

#### **Sourcing Tcl Scripts**

The source command lets you manually load Tcl script files into the Vivado tools:

source <filename>

Where *<filename>* specifies both the name of the file, as well as the relative or absolute path to the file. If no path is specified as part of the file name, then the Vivado tools look for the file in the working directory, or the directory from which the Vivado Design Suite was launched.

Within the Vivado IDE you can also source a Tcl script from the **Tools >Run Tcl Script** menu command.

By default, the source command echoes each line of the file to the Tcl console. This can be prevented by using the -notrace option, which is specific to the Vivado Tcl interpreter:

```

source <filename> -notrace

```

#### Using Tcl Scripts in a Constraints Set

Tcl scripts can be added to project constraint sets like any regular XDC file, except that the XDC files are managed by the tool, and not Tcl scripts. Any constraint defined by a Tcl script and edited by the tool cannot be saved back to the Tcl script automatically. If you need to save your edits, you must export all the constraints in memory to a file and use this file to update your script manually. When opening a design in memory (open\_run), the Tcl scripts are sourced after the XDC files. In a non-project flow, this is equivalent to explicitly sourcing the Tcl scripts after loading the XDC files with read\_xdc. For more information on using XDC files and Tcl scripts in a constraints set, see the *Vivado Design Suite User Guide: Using Constraints* (UG903) [Ref 3].

### **Defining Tcl Hook Scripts**

In a non-project flow you have the ability to source a Tcl script at any point in the flow, such as before or after running the synth\_design command. You can also do this in a project-based flow, using the Vivado IDE, or by using the set\_property command to set a property on either a synthesis or implementation run. Tcl hook scripts allow you to run custom Tcl scripts prior to (tcl.pre) and after (tcl.post) synthesis and implementation design runs, or any of the implementation steps.

Whenever you launch a synthesis or implementation run, the Vivado tools use a predefined Tcl script to process a standard design flow based on the selected strategy. Tcl hook scripts let you customize the standard flow, with pre-processors or post-processors. Being able to add Tcl script processing anywhere in a run can be useful. Every step in the design flow has a pre-hook and post-hook capability. Common uses are:

- Custom reports: timing, power, utilization, or any user-defined Tcl report.

- Modifying the timing constraints for portions of the flow only.

- Modifications to netlist, constraint, or device programming.

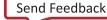

In the GUI you can specify the Tcl hook scripts to be sourced by using the **Change Run Settings** command for the design run. Right-click a run in the **Design Runs** window and select the **Change Run Settings** from the pop-up menu to open the **Design Run Settings** dialog box, shown in Figure 1. The tcl.pre and tcl.post options can be used to specify a Tcl hook script.

| Synthesis Run Properties                                                                         | ? _ [                         |             |    |

|--------------------------------------------------------------------------------------------------|-------------------------------|-------------|----|

| ▷ synth_1                                                                                        | $\leftarrow$                  | <b>\$ 6</b> |    |

| Strategy: Xivado Synthesis Defaults Description: Vivado Synthesis Defaults Synth Design (vivado) | * (Vivado Synthesis 2016) 🗸 🗸 |             | î  |

| tcl.pre                                                                                          |                               |             |    |

| tcl.post*                                                                                        | C:/Data/report.tcl            |             |    |

| -flatten_hierarchy                                                                               | rebuilt                       | ~           |    |

| -gated_clock_conversion                                                                          | off                           | ~           |    |

| -bufg                                                                                            | 12                            |             |    |

| -fanout_limit                                                                                    | 10,000                        |             | U  |

| -directive                                                                                       | Default                       | ~           |    |

| -retiming                                                                                        |                               |             |    |

| -fsm_extraction                                                                                  | auto                          | ~           |    |

| -keep_equivalent_registers                                                                       |                               |             |    |

| -resource_sharing                                                                                | auto                          | ~           |    |

| -control_set_opt_threshold                                                                       | auto                          | ~           |    |

| -no lc                                                                                           |                               |             | Y. |

| General Properties Options Log                                                                   | Reports Messages              |             |    |

Figure 1: Defining Pre and Post Run Tcl Scripts

The Vivado IDE sets a property on the synthesis or implementation run to specify the tcl.pre or tcl.post script to apply before or after the run. You can also set this property directly on a synthesis or implementation run, either in the Tcl Console or as part of a Tcl script.

The properties to set on a synthesis run are:

```

STEPS.SYNTH_DESIGN.TCL.PRE

STEPS.SYNTH_DESIGN.TCL.POST

```

For instance, set the following property to have the report.tcl script launched before synthesis is complete:

```

set_property STEPS.SYNTH_DESIGN.TCL.PRE {C:/Data/report.tcl} [get_runs synth_1]

```

For an implementation run you can define Tcl scripts before and after each step of the implementation process: Opt Design, Power Opt Design, Place Design, Post-Place Power Opt Design, Phys Opt Design, Route Design and Bitstream generation. The properties for each of these are:

STEPS.OPT\_DESIGN.TCL.PRE STEPS.OPT\_DESIGN.TCL.POST STEPS.POWER\_OPT\_DESIGN.TCL.PRE STEPS.POWER\_OPT\_DESIGN.TCL.POST STEPS.PLACE\_DESIGN.TCL.PRE STEPS.PLACE\_DESIGN.TCL.POST STEPS.POST\_PLACE\_POWER\_OPT\_DESIGN.TCL.PRE STEPS.POST\_PLACE\_POWER\_OPT\_DESIGN.TCL.POST STEPS.PHYS\_OPT\_DESIGN.TCL.PRE STEPS.ROUTE\_DESIGN.TCL.PRE STEPS.ROUTE\_DESIGN.TCL.POST STEPS.WRITE\_BITSTREAM.TCL.PRE STEPS.WRITE\_BITSTREAM.TCL.POST

**IMPORTANT:** Relative paths within the tcl.pre and tcl.post scripts are relative to the appropriate run directory of the project they are applied to: <project>/<project.runs>/<run\_name>. You can use the DIRECTORY property of the current project or current run to define the relative paths in your Tcl hook scripts:

get\_property DIRECTORY [current\_project]

get\_property DIRECTORY [current\_run]

#### **Sharing Hook Scripts Between Steps**

When the hook script is step agnostic and only generates a set of reports for an implementation step, it is not efficient to duplicate the script content for each step and just change, for instance, the report file name to match the implementation step. A better way to proceed is to share the same hook script for all the implementation steps and use the Tcl variable ACTIVE\_STEP to build the report filename. This ensures a different file name for each step.

In Project mode, Vivado IDE automatically updates the Tcl variable ACTIVE\_STEP when submitting a run through the run infrastructure to match the implementation step being run.

**Note:** The Tcl variable ACTIVE\_STEP is only available in Project mode while using the run infrastructure.

The following is an example of a hook script using the ACTIVE\_STEP variable:

```

set step $ACTIVE_STEP

report_timing_summary -file tim_summary_${step}.rpt

if {$step == {route_design}} {

report_route_status -file route_status.rpt

}

```

### **Customizing the GUI**

You can use the **Tools > Custom Commands > Customize Commands** menu item to add system or user-defined Tcl commands to the Vivado IDE main menu and toolbar menu. For

www.xilinx.com

more information on adding custom commands to the menu, see this <u>link</u> in the *Vivado Design Suite User Guide: Using the Vivado IDE* (UG893) [Ref 6].

## Writing a Tcl Script

When writing a Tcl script, the emphasis should be, whenever possible, on providing code that can enhance the user experience. This means writing scripts that provide the same type of user experience as the embedded Vivado commands such as providing some type of embedded Help and interactive command line argument. It is also critical to consider all the corner cases that could happen, whether Vivado objects are empty or not after using the get\_\* commands and so forth. It is also common when writing Tcl code, to create some lower-level procedures that are used in the code. To avoid name collision of procedures and global variables, Xilinx recommends that you develop the code within its own namespace so that name collisions are minimized.

#### **Defining Tcl Procedures**

Because the Vivado Design Suite provides a full Tcl interpreter built into the tool, creating new custom commands and procedures is a simple task. You can write Tcl scripts that can be loaded and run from the Vivado IDE, or you can write procedures (or procs), to act like new Tcl commands, taking arguments, checking for errors, and returning results.

A Tcl procedure is defined with the proc command which takes three arguments: the procedure name, the list of arguments, and the body of code to be executed. The following code provides a simple example of a procedure definition:

```

proc helloProc { arg1 } {

# This is a comment inside the body of the procedure

puts "Hello World! Arg1 is $arg1"

}

```

**TIP:** Although the curly braces are optional for the argument definition of this procedure, since helloProc has only one argument, it makes the procedure definition easier to read by enclosing the arguments in braces. The braces are required when the procedure accepts multiple arguments.

A procedure usually has predefined arguments. Each of them can optionally have a default value. When an argument has a default value, it does not need to be specified when calling the procedure if all the mandatory preceding arguments are specified. A procedure returns an empty string unless the return command is used to return a different value. The following example defines a procedure, reportWorstViolations, with three arguments:

```

proc reportWorstViolations { nbrPaths corner delayType } {

report_timing -max_paths $nbrPaths -corner $corner -delay_type $delayType -nworst 1

}

```

When running the procedure, all the arguments must be specified as shown:

%> reportWorstViolations 2 Slow max

%> reportWorstViolations 10 Fast min

The next example is a different form of the same procedure, where the last two of the three arguments have a default value. The default value for corner is *Slow*, and the default value for delayType is *Max*. With default values specified in the definition of the procedure, the corner and delayType arguments are optional when calling the procedure.

```

proc reportWorstViolations { nbrPaths { corner Slow } { delayType Max } } {

report_timing -max_paths $nbrPaths -corner $corner -delay_type $delayType -nworst 1

}

```

When running this procedure, all of the following calls of the command are valid:

```

%> reportWorstViolations 2

%> reportWorstViolations 10 Fast

%> reportWorstViolations 10 Slow Min

```

The following example is an illustration of a procedure that has one mandatory argument, nbrPath, but that can also accept any number of additional arguments. This uses the Tcl keyword args in the list of arguments when defining the procedure. The args keyword is a Tcl list that can have any number of elements, including none.

```

proc reportWorstViolations { nbrPaths args } {

eval report_timing -max_paths $nbrPaths $args

}

```

When executing a Tcl command, you can use variable substitution to replace some of the command line arguments accepted or required by the Tcl command. In this case, you must use the Tcl eval command to evaluate the command line with the Tcl variable as part of the command. In the preceding example, the variable list of arguments (\$args) is passed to the encapsulated report\_timing command as a variable, and so requires the use of the eval command.

When running this procedure, any of the following forms of the command will work:

```

%> reportWorstViolations 2

%> reportWorstViolations 1 -to [get_ports]

%> reportWorstViolations 10 -delay_type min_max -nworst 2

```

In the first example, the number 2 is passed to the *snbrPaths* argument, and applied to -max\_paths. In the second and third examples, the numbers 1 and 10 respectively are applied to -max\_paths, and all the subsequent characters are assigned to *sargs*.

The following example provides the procedure definition for the reportCriticalPaths command that was previously used in the Non-Project Mode example script. The procedure takes a single argument, \$filename, and has been commented to explain each section:

```

#_____

# reportCriticalPaths

#_____

# This function generates a CSV file that provides a summary of the first

# 50 violations for both Setup and Hold analysis. So a maximum number of

# 100 paths are reported.

#_____

proc reportCriticalPaths { fileName } {

# Open the specified output file in write mode

set FH [open $fileName w]

# Write the current date and CSV format to a file header

puts $FH "#\n# File created on [clock format [clock seconds]]\n#\n"

puts $FH "Startpoint,Endpoint,DelayType,Slack,#Levels,#LUTs"

# Iterate through both Min and Max delay types

foreach delayType {max min} {

# Collect details from the 50 worst timing paths for the current analysis

# (max = setup/recovery, min = hold/removal)

# The $path variable contains a Timing Path object.

foreach path [get_timing_paths -delay_type $delayType -max_paths 50 -nworst 1] {

# Get the LUT cells of the timing paths

set luts [get_cells -filter {REF_NAME =~ LUT*} -of_object $path]

# Get the startpoint of the Timing Path object

set startpoint [get_property STARTPOINT_PIN $path]

# Get the endpoint of the Timing Path object

set endpoint [get_property ENDPOINT_PIN $path]

# Get the slack on the Timing Path object

set slack [get_property SLACK $path]

# Get the number of logic levels between startpoint and endpoint

set levels [get_property LOGIC_LEVELS $path]

# Save the collected path details to the CSV file

puts $FH "$startpoint,$endpoint,$delayType,$slack,$levels,[llength $luts]"

}

}

# Close the output file

close $FH

puts "CSV file $fileName has been created.\n"

return 0

}; # End PROC

```

#### **Parsing Command Line Arguments**

It can be useful and sometimes necessary to write procedures that use external parameters or arguments as they can broaden the spectrum of usage of the procedure without having to write too much redundant code. A single procedure that can handle multiple contexts is easier to use and maintain that multiple procedures that cover the same range of contexts with duplicated code.

This is especially useful when the procedure is being used interactively. It is a lot friendlier for the user to be able to specify some command line options like with any Vivado commands.

Tcl provides an easy way to do this through the args variable. The keyword args used inside the list of arguments of a procedure can match any number of elements, including none. The args variable is a regular Tcl list that can be processed and analyzed like any Tcl list.

There are multiple techniques to parse the command line arguments, and the example code below shows just one of them:

```

01 proc lshift listVar {

02 upvar 1 $listVar L

03

set r [lindex $L 0]

04

set L [lreplace $L [set L 0] 0]

05

return $r

06 }

07

08

09 proc myproc { args } {

10

11

#------

12

# Process command line arguments

13

#-----

set error O

14

15

set help 0

16

set verbose 0

17 set ports {}

18 # if {[llength $args] == 0} { incr help }; # Uncomment if necessary

19 while {[llength $args]} {

set flag [lshift args]

20

21

switch -exact -- $flag {

22

-p -

23

-ports {

24

set ports [lshift args]

25

}

26

-v -

27

-verbose {

28

set verbose 1

29

}

30

-h -

31

-help {

32

incr help

}

33

34

default {

```

```

35

if {[string match "-*" $flag]} {

36

puts " ERROR - option '$flag' is not a valid option."

37

incr error

38

} else {

39

puts "ERROR - option '$flag' is not a valid option."

40

incr error

41

}

42

}

43

}

44

}

45

46

if {$help} {

47

set callerflag [lindex [info level [expr [info level] -1]] 0]

48

# <-- HELP

49

puts [format {

50

Usage: %s

[-ports|-p <listOfPorts>]

51

52

[-verbose|-v]

53

[-help|-h]

54

55

Description: xxxxxxxxxxxxxxxxxxxxxxx

56

57

58

Example:

59

%s -port xxxxxxxxxxxxxxx

60

61 } $callerflag $callerflag ]

62

# HELP -->

63

return -code ok {}

64

3

65

66

# Check validity of arguments. Increment $error to generate an error

67

68

if {$error} {

69

return -code error {Oops, something is not correct}

70

}

71

72

# Do something

73

74

return -code ok {}

75 }

```

#### **Explanations:**

- 1. Lines 1-6: Definition for the lshift procedure that removes the first element of a list.

- Line 9: myproc is defined with a single argument, args, that can take any number of elements. In this example code, myproc supports three command line options: -ports <string> / -verbose / -help.

- 3. Lines 19-44: Loop through all the command line arguments. When all the arguments have been processed, the args variable is empty.

- Line 20: The command line argument that needs to be processed is saved inside the flag variable. Use the lshift proc to get the argument and remove it from the args variable.

www.xilinx.com

5. Lines 21-43: Check the content of the flag variable against all the valid arguments. The switch statement uses the -exact option so that the full option name is checked against the content of flag. For example, to define the ports, the user needs to specify -p or -ports.

The -p/-ports option takes a command line argument that is being read and removed from the list args with lshift args (line 24).

The -v/-verbose option is just a boolean and therefore does not need any additional argument from args (line 28).

Lines 31-33: Check for the -h/-help options.

Lines 36-38: Check for any command line argument starting with "-" (without quotes). In this sample proc, they are not supported.

Lines 39-40: Check for a command line argument that does not start with "-" (without quotes). In this example proc, they are not supported.

- 6. Lines 46-64: Display the embedded Help if -h/-help has been specified. Those lines as well as lines 30-33 can be removed if the proc does not need to provide any embedded Help.

- 7. Lines 68-70: Check if any error has occurred. Typically, some additional code to check the validity of the arguments should happen before line 68. If there would be any error or, for example, incompatibility between the command line options provided by the user, then the error variable could be incremented which would then trigger line 69.

- 8. Line 73 and beyond: Add your code here

The above code parses the command line arguments and searches for an exact match with the supported options (line 21). However, there are some cases when it might be better to match the command line arguments against some expressions instead of searching for an exact match. This is done by using the -glob switch instead of the -exact switch on line 21. See the following example.

```

21 switch -glob -- $flag {

-p* -

22

23

-ports {

24

set ports [lshift args]

25

}

-v* -

26

27

-verbose {

28

set verbose 1

29

}

-h* -

30

31

-help {

32

incr help

33

}

34

default {

if {[string match "-*" $flag]} {

35

puts " ERROR - option '$flag' is not a valid option."

36

```

Lines 22, 26 and 30 illustrate some expressions using the "\*" as a wildcard. The above code matches any string starting with -p as a valid command line option to define the ports, for example -pfoo.

Although the example procedure, myproc, is acceptable for an interactive command, it has some runtime overhead due to the parsing of the arguments. The runtime overhead might not be acceptable for a low-level procedure that is called many times. A different technique can be used to add some command line arguments to a procedure that needs very little runtime overhead. This is done by assigning the list of commands line arguments to a Tcl array. However, this implies that each command line option has one and only one argument. See the following example.

```

01 proc myproc2 { args } {

02

# Default values

03 set defaults [list -p 123 -v 0]

# First, assign default values

04

array set options $defaults

05

# Then, override with user choice

06

07

array set options $args

08

09

set ports $options(-p)

10

set verbose $options(-v)

11

set error 0

12

13

# Check validity of arguments. Increment $error to generate an error

14

15

if {$error} {

16

return -code error {Oops, something is not correct}

17

}

18

19

# Do something

20

21

return -code ok {}

22 }

```

**Explanations:**

- 1. Line 1: myproc2 is defined with a single argument, args, that can take any number of elements. However, since args is used later on to set a Tcl array, it must have an even number of arguments.

- 2. Line 3: Default values for the various options. Each option has one and only one value.

- 3. The format of the list is:

<option1> <valueForOption1> <option2> <valueForOption2> ... <optionN> <valueForOptionN>

4. Line 5: The Tcl array options is initialized with the default values.

- 5. Line 7: The args variable overrides the default values

- 6. Line 9-10: The value of each option is being read with \$options(<option>). It is also

possible to check that an option exist with the following.

```

if [info exists options(<option>)] { ... }

```

**Note:** The command line options that are working as a flag and have no intrinsic value are easily implemented by passing, for example, a value of 0 or 1 with the option. In the previous example procedure, the flag -v is turned on with: myproc2 -v 1.

#### Local and Global Variables

A local variable is a variable created inside a procedure. It is created at runtime inside the stack of the function. The variable is only accessible within the procedure and the variable name is not subject to name collision with variable names outside of the procedure. This means that, for example, a local variable  $f_{00}$  created inside a procedure is different from a variable  $f_{00}$  created outside of the procedure and both variables have independent content. A local variable is created with the set Tcl keyword like any other variable.

The parameters defined as the arguments of a procedure are, by default, local variables. Whenever a procedure is called (for example reportCriticalPaths \$myfilename), the content of the calling variables (for example \$myfilename) are copied inside the stack of the procedure. If the calling variables are Tcl lists with a large number of elements, this mechanism has a runtime and memory penalty. There are also some scenarios when it is necessary to modify the content of the caller variables. Tcl provides a way to do that by passing a variable name as a reference instead of passing the content of the variable. Once a variable is passed as a reference, any modification of the variable inside the procedure directly modifies the caller's variable inside the caller's space. The keyword upvar is used inside the body of the procedure to define a parameter that is passed as reference. The procedure 1shift that has been introduced earlier uses this technique:

```

proc lshift {listVar} {

upvar 1 $listVar L

set r [lindex $L 0]

set L [lreplace $L [set L 0] 0]

return $r

}

```

In the example proc myproc, lshift is called by passing the variable name args instead of the content <code>\$args</code>.

A global variable is a variable created outside of a procedure and that belongs to the global namespace. To refer to a global variable inside a procedure, the keyword global is used followed by the variable name:

```

proc printEnv {} {

global env

foreach var [lsort [array names env]] { puts " $var = $env($var)" }

}

```

The above example defines a procedure printEnv that prints the system environment variables. The Tcl array, env is a global variable initialized when the Vivado tools start. The printEnv procedure refers to the global env variable through the global env command. After the global variable is declared, it is accessed like any local variable. The global variable can be read and modified.

Another way to access a global variable is to specify the namespace qualifier with it. The namespace qualifier for the global namespace is "::" (without any quotes) and therefore a procedure can refer to the global variable env with ::env. The syntax is the same for any global variable. For example:

```

proc printEnv {} {

foreach var [lsort [array names ::env]] { puts " $var = $::env($var)" }

}

```

Since printEnv specifies the full path to the env variable, the procedure does not need to declare global env.

**Note:** Xilinx does not recommend that you use global variables as they rely on variable names created outside the scope of the procedure. Global variables are sometimes used to avoid having to pass large Tcl lists to a procedure. The upvar technique should always be considered before using a global variable.

**Note:** When using the run infrastructure in Project mode, it is not possible to share global variables defined inside the Vivado environment with the hook scripts. Refer to Getting User's Input for recommended methods to share information between scripts.

**Note:** The close\_project and close\_design commands do not change the state of the Tcl interpreter. All the global variables and user created namespaces are persistent after running those commands.

#### **Namespaces for Procedures**

By default, every procedure created inside the Tcl interpreter is created inside the global namespace. A disadvantage of this is potential conflicts with the procedure or variable names when multiple Tcl scripts from different sources are being used. In addition, the global namespace is also being polluted by procedure names that might be only be used by some other procedures and that are not meant to be directly accessed by the user.

Instead of defining all the variables and procedures in the global namespace, Tcl supports the concept of namespace that encompasses variables and procedures inside a more private scope. Namespaces can also be nested, so a namespace can be defined inside another namespace without restriction on the number of levels of scoping. Namespaces add a new syntax to procedure and variable names. A double-colon, ::, separates the namespace name from the variable or procedure name.

Below is an example that illustrates how a namespace is created and how procedures and variables are assigned to the namespace. This example creates a namespace, foo that reproduces the functionality of a small stack with 2 public procedures (push and pop):

www.xilinx.com

```

01 namespace eval foo {

02 variable stack [list]

03 variable count 0

04

variable params

05

array set params [list var1 value1 var2 value2 var3 value3]

06

07

namespace export push pop

08

proc push { args } {

09

variable stack

10

variable count

11

12

lappend stack $args

13

incr count

14

}

15

16

proc pop {} {

variable stack

17

18

variable count

19

if {[llength $stack] > 0} {

20

set value [lindex $stack end]

21

set stack [lrange $stack 0 end-1]

22

incr count -1

return $value

23

24

} else {

error " no more element in the stack"

25

26

}

27

}

28

29 }

30

31 proc foo::dump {} {

32

variable stack

33

variable count

34

if {[llength $stack] > 0} {

puts " There are $count element(s) in the stack:"

35

36

foreach element $stack {

puts "

37

$element"

38

}

39

return 0

40

} else {

error " no element in the stack"

41

42

}

43 }

44

45 namespace import foo::*

```

#### **Explanations:**

1. The namespace is defined with the command:

namespace eval <name> { ... }

- 2. Line 1 declares the namespace,  $f_{00}$  and line 29 is the closing curly bracket of the namespace definition.

- 3. Variables inside the namespace are created with the command variable (lines 2-4):

```

variable <varname> ?<varvalue>?

```

A Tcl array cannot be initialized with the variable command. It needs to be created first (line 4) and initialized afterward (line 5).

**Note:** Do not use the set command to declare variables inside a namespace as it will confuse the Tcl interpreter in the case the same variable name exists in the global namespace.

4. Procedures can be created directly inside the namespace definition or outside. When a procedure is created within the command, namespace eval ... { ... }, it does not need to have the namespace qualifier in the name (in this example foo::).

Lines 9 and 16: push and pop are created inside the namespace definition

- 5. Procedures can also be created outside of the namespace definition and added to the namespace by using the full namespace qualifier prepended to the procedure name. In the above example, the procedure dump (line 31) is created output of the namespace definition but added to the namespace foo.

- 6. Lines 10-11, 17-18, 32-33: Procedures refer to variables created inside the namespace using the keyword variable.

- 7. A procedure created inside a namespace can be accessed with the full namespace qualifier, for example foo::push, foo::pop and foo::dump. From within the namespace itself, the namespace qualifier is not needed when referring to procedures from the same namespace. For instance, if the procedure dump needs to call push, it does not need to specify foo::push, but just push.

Here is an example usage of the namespace foo:

```

vivado% foo::push This is a test

1

vivado% foo::push {This is another line}

2

vivado% push This is the third line

3

vivado% foo::dump

There are 3 element(s) in the stack:

This is a test

{This is another line}

This is the third line

0

```

```

vivado% puts "The last element stacked is: [foo::pop]"

The last element stacked is: This is the third line

vivado% puts "The previous element stacked is: [pop]"

The previous element stacked is: {This is another line}

vivado% foo::dump

There are 1 element(s) in the stack:

This is a test

0

vivado% dump

invalid command name "dump"

```

#### **Template Script**

Below is a template script based on the notions that been introduced earlier. It illustrates:

- 1. Usage of a private namespace to avoid polluting the global namespace (lshift is only available inside the namespace foo).

- 2. Handling of command line arguments (including -help and -version to provide a version of the script).

- 3. Usage of return -error (or error) command to generate Tcl errors when it is needed

```

namespace eval foo {

namespace export myproc

variable version 1.0

}

proc foo::lshift listVar {

upvar 1 $listVar L

set r [lindex $L 0]

set L [lreplace $L [set L 0] 0]

return $r

}

proc foo::myproc { args } {

#_____

# Process command line arguments

set error 0

set help 0

set verbose 0

set ports {}

# if {[llength $args] == 0} { incr help }; # Uncomment if necessary

while {[llength $args]} {

set flag [lshift args]

switch -exact -- $flag {

-p -

-ports {

set ports [lshift args]

}

-v -

-verbose {

set verbose 1

}

```

```

-h -

-help {

incr help

}

-version {

variable version

return $version

}

default {

if {[string match "-*" $flag]} {

puts " ERROR - option '$flag' is not a valid option."

incr error

} else {

puts "ERROR - option '$flag' is not a valid option."

incr error

}

}

}

}

if {$help} {

set callerflag [lindex [info level [expr [info level] -1]] 0]

# <-- HELP

puts [format {

Usage: %s

[-ports|-p <listOfPorts>]

[-verbose|-v]

[-version]

[-help|-h]

Description: xxxxxxxxxxxxxxxxxx.

********************************

Example:

%s -port xxxxxxxxxxxxxxx

} $callerflag $callerflag ]

# HELP -->

return -code ok {}

}

# Check validity of arguments. Increment $error to generate an error

if {$error} {

return -code error {Oops, something is not correct}

}

# Do something

return -code ok {}

}

```

www.xilinx.com

## **Accessing Design Objects**