# Vivado Design Suite Tcl Command Reference Guide

UG835 (v2017.1) April 5, 2017

# **Revision History**

### Commands Deprecated as of 2017.1

- get\_gtbanks: Use 'get\_iobanks -filter {BANK\_TYPE == BT\_MGT}' instead.

- **open\_netlist\_design**: Use 'link\_design' or 'open\_run' instead.

- read\_vcd:

#### Commands Added in 2017.1

auto\_detect\_xpm, config\_hw\_sio\_gts, make\_bd\_intf\_pins\_external, make\_bd\_pins\_external, report\_pr\_configuration\_analysis, update\_smartcable, write\_dsa\_rom

#### Commands Modified in 2017.1

config\_webtalk, get\_pplocs, get\_waves, move\_wave, remove\_wave, report\_sim\_device, validate\_dsa

# Introduction

## Overview of Tcl Capabilities in Vivado

The Tool Command Language (Tcl) is the scripting language integrated in the Vivado® tool environment. Tcl is a standard language in the semiconductor industry for application programming interfaces, and is used by Synopsys® Design Constraints (SDC).

SDC is the mechanism for communicating timing constraints for FPGA synthesis tools from Synopsys Synplify as well as other vendors, and is a timing constraint industry standard; consequently, the Tcl infrastructure is a "Best Practice" for scripting language.

Tcl lets you perform interactive queries to design tools in addition to executing automated scripts. Tcl offers the ability to "ask" questions interactively of design databases, particularly around tool and design settings and state. Examples are: querying specific timing analysis reporting commands live, applying incremental constraints, and performing queries immediately after to verify expected behavior without re-running any tool steps.

The following sections describe some of the basic capabilities of Tcl with Vivado.

**NOTE:** This manual is not a comprehensive reference for the Tcl language. It is a reference to the specific capabilities of the Vivado Design Suite Tcl shell, and provides reference to additional Tcl programming resources.

## **Launching the Vivado Design Suite**

You can launch the Vivado Design Suite and run the tools using different methods depending on your preference. For example, you can choose a Tcl script-based compilation style method in which you manage sources and the design process yourself, also known as Non-Project Mode. Alternatively, you can use a project-based method to automatically manage your design process and design data using projects and project states, also known as Project Mode. Either of these methods can be run using a Tcl scripted batch mode or run interactively in the Vivado IDE. For more information on the different design flow modes, see the *Vivado Design Suite User Guide: Design Flows Overview (UG892)*.

#### Tcl Shell Mode

If you prefer to work directly with Tcl commands, you can interact with your design using Tcl commands with one of the following methods:

- Enter individual Tcl commands in the Vivado Design Suite Tcl shell outside of the Vivado IDE.

- Enter individual Tcl commands in the Tcl Console at the bottom of the Vivado IDE.

- Run Tcl scripts from the Vivado Design Suite Tcl shell.

- Run Tcl scripts from the Vivado IDE.

Use the following command to invoke the Vivado Design Suite Tcl shell either at the Linux command prompt or within a Windows Command Prompt window:

vivado -mode tcl

**TIP:** On Windows, you can also select **Start > All Programs > Xilinx Design Tools > Vivado yyyy.x > Vivado yyyy.x Tcl Shell**, where "yyyy.x" is the installed version of Vivado.

For more information about using Tcl and Tcl scripting, see the *Vivado Design Suite User Guide: Using the Tcl Scripting Capabilities (UG894).* For a step-by-step tutorial that shows how to use Tcl in the Vivado tool, see the *Vivado Design Suite Tutorial: Design Flows Overview (UG888).*

#### Tcl Batch Mode

You can use the Vivado tools in batch mode by supplying a Tcl script when invoking the tool. Use the following command either at the Linux command prompt or within a Windows Command Prompt window:

vivado -mode batch -source <your Tcl script>

The Vivado Design Suite Tcl shell will open, run the specified Tcl script, and exit when the script completes. In batch mode, you can queue up a series of Tcl scripts to process a number of designs overnight through synthesis, simulation, and implementation, and review the results on the following morning.

#### Vivado IDE Mode

If you prefer to work in a GUI, you can launch the Vivado IDE from Windows or Linux. For more information on the Vivado IDE, see the *Vivado Design Suite User Guide: Using the Vivado IDE (UG893)*.

Launch the Vivado IDE from your working directory. By default the Vivado journal and log files, and any generated report files, are written to the directory from which the Vivado tool is launched. This makes it easier to locate the project file, log files, and journal files, which are written to the launch directory.

In the Windows OS, select **Start > All Programs > Xilinx Design Tools > Vivado yyyy.x > Vivado yyyy.x Tcl Shell**, where "yyyy.x" is the installed version of Vivado.

**TIP:** You can also double-click the Vivado IDE shortcut icon on your Windows desktop.

In the Linux OS, enter the following command at the command prompt:

vivado -or- vivado -mode gui

If you need help, with the Vivado tool command line executable, type:

vivado -help

If you are running the Vivado tool from the Vivado Design Suite Tcl shell, you can open the Vivado IDE directly from the Tcl shell by using the start gui command.

From the Vivado IDE, you can close the Vivado IDE and return to a Vivado Tcl shell by using the stop\_gui command.

#### Tcl Journal Files

When you invoke the Vivado tool, it writes the <code>vivado.log</code> file to record the various commands and operations performed during the design session. The Vivado tool also writes a file called <code>vivado.jou</code> which is a journal of just the Tcl commands run during the session. The journal file can be used as a source to create new Tcl scripts.

**NOTE:** Backup versions of the journal file, named <code>vivado\_<id>.backup.jou</code>, are written to save the details of prior runs whenever the Vivado tool is launched. The <code><id></code> is a unique identifier that allow the tool to create and store multiple backup versions of the log and journal files

#### Tcl Help

The Tcl help command provides information related to the supported Tcl commands.

help – Returns a list of Tcl command categories.

help

Command categories are groups of commands performing a specific function, like File I/O for instance.

help -category category - Returns a list of commands found in the specified category.

```

help -category object

```

This example returns the list of Tcl commands for handling objects.

• help pattern – Returns a list of commands that match the specified search pattern. This form can be used to quickly locate a specific command from a group of commands.

```

help get *

```

This example returns the list of Tcl commands beginning with get\_.

help command – Provides detailed information related to the specified command.

```

help get cells

```

This example returns specific information of the get cells command.

• help -args command - Provides an abbreviated help text for the specified command, including the command syntax and a brief description of each argument.

```

help -args get cells

```

• help -syntax command - Reports the command syntax for the specified command.

```

help -syntax get cells

```

## **Scripting in Tcl**

#### Tcl Initialization Scripts

**TIP:** The following describes where you can place <code>Vivado\_init.tcl</code> scripts if you would like to customize Vivado on startup. No <code>Vivado\_init.tcl</code> scripts are provided in the Vivado release by default.

When you start the Vivado tool, it looks for a Tcl initialization script in three different locations, each one overriding the last one found:

- 1. Enterprise: In the software installation directory, installdir/Vivado/version/scripts/Vivado init.tcl

- 2. Vivado Version: In a local user directory, for a specific version of the Vivado Design Suite:

- For Windows 7: %APPDATA%/Xilinx/Vivado/version/Vivado init.tcl

- For Linux: \$HOME/.Xilinx/Vivado/version/Vivado\_init.tcl

- 3. Vivado User: In a local user directory, for the general Vivado Design Suite:

- For Windows 7: %APPDATA%/Xilinx/Vivado/Vivado\_init.tcl

- For Linux: \$HOME/.Xilinx/Vivado/Vivado init.tcl

#### Where:

installdir is the installation directory where the Vivado Design Suite is installed.

If Vivado\_init.tcl exists, in one or all of these locations, the Vivado tool sources this file, in the order described above.

- The Vivado\_init.tcl file in the installation directory allows a company or design group to support a common initialization script for all users. Anyone starting the Vivado tool from that installation location sources the enterprise Vivado init.tcll script.

- A user's <code>Vivado\_init.tcl</code> file in the home directory allows each user to specify additional commands, or to override commands from the software installation to meet their specific design requirements.

- No Vivado\_init.tcl file is provided with the Vivado Design Suite installation. You must create the Vivado\_init.tcl file and place it in either the installation directory, or your home directory, as discussed to meet your specific needs.

**TIP:** Other tools in the Vivado Design Suite also support initialization scripts in the following form: tool\_init.tcl, where tool can include Vivado, vivado\_lab, xsim, and xelab.

The <code>Vivado\_init.tcl</code> file is a standard Tcl command file that can contain any valid Tcl command supported by the Vivado tool. You can also source another Tcl script file from within <code>Vivado init.tcl</code> by adding the following statement:

source path to file/file name.tcl

**NOTE:** You can also specify the -init option when launching the Vivado Design Suite from the command line. Type vivado -help for more information.

#### Sourcing a Tcl Script

A Tcl script can be sourced from either one of the command-line options or from the GUI. Within the Vivado Integrated Design Environment (IDE) you can source a Tcl script from Tools > Run Tcl Script.

You can source a Tcl script from a Tcl command-line option:

source file\_name

When you invoke a Tcl script from the Vivado IDE, a progress bar is displayed and all operations in the IDE are blocked until the scripts completes.

There is no way to interrupt script execution during run time; consequently, standard OS methods of killing a process must be used to force interruption of the tool. If the process is killed, you lose any work done since your last save.

Typing help source in the Tcl console will provide additional information regarding the source command.

#### Using Tcl.pre and Tcl.post Hook Scripts

Tcl Hook scripts allow you to run custom Tcl scripts prior to (tcl.pre) and after (tcl.post) synthesis and implementation design runs, or any of the implementation steps. Whenever you launch a run, the Vivado tool uses a predefined Tcl script which executes a design flow based on the selected strategy. Tcl Hook scripts let you customize the standard flow, with pre-processors or post-processors, such as for generating custom reports. The Tcl Hook script must be a standard Tcl script.

Every step in the design flow has a pre- and post-hook capability. Common examples are:

- Custom reports: timing, power, utilization, or any user-defined tcl report.

- Temporary parameters for workarounds.

- Over-constraining timing constraints for portions of the flow.

- Multiple iterations of stages (e.g. multiple calls to phys\_opt\_design).

- Modifications to netlist, constraint, or device programming.

get\_property DIRECTORY [current\_project] get\_property DIRECTORY [current\_run]

For more information on defining Tcl Hook scripts, refer to the *Vivado Design Suite User Guide: Using Tcl Scripting (UG894)*.

## **General Tcl Syntax Guidelines**

Tcl uses the Linux file separator (/) convention regardless of which Operating System you are running.

The following subsections describe the general syntax guidelines for using Tcl in the Vivado Design Suite.

## **Using Tcl Eval**

When executing Tcl commands, you can use variable substitution to replace some of the command line arguments accepted or required by the Tcl command. However, you must use the Tcl eval command to evaluate the command line with the Tcl variable as part of the command.

For instance, the help command can take the <code>-category</code> argument, with one of a number of command categories as options:

```

help -category ipflow

```

You can define a variable to hold the command category:

```

set cat "ipflow"

```

#### Where:

- set is the Tcl keyword that defines the variable.

- cat is the name of the variable being defined.

- "ipflow" is the value assigned to the variable.

You can then evaluate the variable in the context of the Tcl command:

```

eval help -category $cat

or,

set cat "category ipflow" eval help $cat

You can also use braces {} in place of quotation marks "" to achieve the same result:

```

```

set runblocksOptDesignOpts { -sweep -retarget -propconst -remap }

eval opt_design $runblocksOptDesignOpts

```

Typing help eval in the Tcl console will provide additional information regarding the eval command.

## **Using Special Characters**

Some commands take arguments that contain characters that have special meaning to Tcl. Those arguments must be surrounded with curly braces {} to avoid unintended processing by Tcl. The most common cases are as follows.

**Bus Indexes** - Because square brackets [] have special meaning to Tcl, an indexed (bit- or part-selected) bus using the square bracket notation must be surrounded with curly braces. For example, when adding index 4 of a bus to the Vivado Common Waveform Viewer window using the square bracket notation, you must write the command as:

```

add wave {bus[4]}

```

Parentheses can also be used for indexing a bus, and because parentheses have no special meaning to Tcl, the command can be written without curly braces. For example:

```

add wave bus (4)

```

**Verilog Escaped Identifiers** - Verilog identifiers containing characters or keywords that are reserved by Verilog need to be "escaped" both in the Verilog source code and on the simulator command line by prefixing the identifier with a backslash "\" and appending a space. Additionally, on the Tcl command line the escaped identifier must be surrounded with curly braces.

**NOTE:** If an identifier already includes a curly brace, then the technique of surrounding the identifier with curly braces does not work, because Tcl interprets curly braces as reserved characters even nested within curly braces. Instead, you must use the technique described below, in **VHDL Extended Identifiers**.

For example, to add a wire named "my wire" to the Vivado Common Waveform Viewer window, you must write the command as:

```

add wave {\my wire }

```

**NOTE:** Be sure to append a space after the final character, and before the closing brace.

Verilog allows any identifier to be escaped. However, on the Tcl command line do not escape identifiers that are not required to be escaped. For example, to add a wire named "w" to the Vivado Common Waveform Viewer window, the Vivado simulator would not accept:

```

add wave {\w }

```

as a valid command, since this identifier (the wire name "w") does not required to be escaped. The command must be written as:

```

add wave w

```

VHDL Extended Identifiers - VHDL extended identifiers contain backslashes, "\", which are reserved characters in Tcl. Because Tcl interprets a backslash next to a close curly brace \} as being a close curly brace character, VHDL extended identifiers cannot be written with curly braces. Instead, the curly braces must be absent and each special character to Tcl must be prefixed with a backslash. For example, to add the signal \my sig\ to the Wave window, you must write the command as:

```

add wave \\my\ sig\\

```

**NOTE:** Both the backslashes that are part of the extended identifier, and the space inside the identifier are prefixed with a backslash.

## **General Syntax Structure**

The general structure of Vivado Design Suite Tcl commands is:

```

command [optional parameters] required parameters

```

Command syntax is of the verb-noun and verb-adjective-noun structure separated by the underscore ("\_") character.

Commands are grouped together with common prefixes when they are related.

- Commands that guery things are generally prefixed with get\_.

- Commands that set a value or a parameter are prefixed with set.

- Commands that generate reports are prefixed with report\_.

The commands are exposed in the global namespace. Commands are "flattened," meaning there are no "sub-commands" for a command.

## **Example Syntax**

The following example shows the return format on the get cells -help command:

```

get cells

Description:

Get a list of cells in the current design

Syntax:

get cells [-hsc <arg>] [-hierarchical] [-regexp] [-nocase] [-filter <arg>]

[-of objects <args>] [-match style <arg>] [-quiet] [-verbose]

[<patterns>]

Returns:

list of cell objects

Usage:

Name

Description

_____

Hieraron,

Default: /

[-hsc]

Hierarchy separator

[-hierarchical] Search level-by-level in current instance

[-regexp] Patterns are full regular expressions

[-nocase] Perform case-insensitive matching (valid only when -regexp

specified)

[-filter] Filter list with expression

[-of_objects] Get cells of these pins, timing paths, nets, bels, sites

or drc violations

[-match_style] Style of pattern matching

Default: sdc

Values: ucf, sdc

[-quiet] Ignore command errors

[-verbose] Suspend message limits during command execution

[<patterns>] Match cell names against patterns

Default: *

Categories:

SDC, XDC, Object

```

#### **Unknown Commands**

Tcl contains a list of built-in commands that are generally supported by the language, Vivado tool specific commands which are exposed to the Tcl interpreter, and user-defined procedures.

Commands that do not match any of these known commands are sent to the OS for execution in the shell from the exec command. This lets users execute shell commands that might be OS-specific. If there is no shell command, then an error message is issued to indicate that no command was found.

#### **Return Codes**

Some Tcl commands are expected to provide a return value, such as a list or collection of objects on which to operate. Other commands perform an action but do not necessarily return a value that can be used directly by the user. Some tools that integrate Tcl interfaces return a 0 or a 1 to indicate success or error conditions when the command is run.

To properly handle errors in Tcl commands or scripts, you should use the Tcl built-in command catch. Generally, the catch command and the presence of numbered info, warning, or error messages should be relied upon to assess issues in Tcl scripted flows.

Vivado tool Tcl commands return either TCL\_OK or TCL\_ERROR upon completion. In addition, the Vivado Design Suite sets the global variable \$ERRORINFO through standard Tcl mechanisms.

To take advantage of the \$ERRORINFO variable, use the following line to report the variable after an error occurs in the Tcl console:

```

puts $ERRORINFO

```

This reports specific information to the standard display about the error. For example, the following code example shows a Tcl script (procs.tcl) being sourced, and a user-defined procedure (loads) being run. There are a few transcript messages, and then an error is encountered at line 5.

```

Line 1: Vivado % source procs.tcl

Line 2: Vivado% loads

Line 3: Found 180 driving FFs

Line 4: Processing pin a_reg_reg[1]/Q...

Line 5: ERROR: [HD-Tcl 53] Cannot specify '-patterns' with '-of_objects'.

Line 6: Vivado% puts $errorInfo

Line 7: ERROR: [HD-Tcl 53] Cannot specify '-patterns' with '-of_objects'.

While executing "get_ports -of objects $pin" (procedure "my_report" line 6) invoked from within procs.tcl

```

You can add puts \$ERRORINFO into catch clauses in your Tcl script files to report the details of an error when it is caught, or use the command interactively in the Tcl console immediately after an error is encountered to get the specific details of the error.

In the example code above, typing the puts \$ERRORINFO command in line 6, reports detailed information about the command and its failure in line 7.

## First Class Tcl Objects and Relationships

The Tcl commands in the Vivado Design Suite provide direct access to the object models for netlist, devices, and projects. These are Vivado first-class objects, which means they are more than just a string representation, and they can be operated on and queried. There are a few exceptions to this rule, but generally "things" can be queried as objects, and these objects have properties that can be queried and they have relationships that allow you to get to other objects.

## **Object Types and Definitions**

There are many object types in the Vivado Design Suite; this chapter provides definitions and explanations of the basic types. The most basic and important object types are associated with entities in a design netlist, and these types are listed in the following subsections:

#### Cell

A cell is an instance, either primitive or hierarchical inside a netlist. Examples of cells include flip-flops, LUTs, I/O buffers, RAM and DSPs, as well as hierarchical instances which are wrappers for other groups of cells.

#### Pin

A pin is a point of logical connectivity on a cell. A pin allows the internals of a cell to be abstracted away and simplified for easier use, and can either be on hierarchical or primitive cells. Examples of pins include clock, data, reset, and output pins of a flop.

#### Port

A port is a special type of hierarchical pin, a pin on the top level netlist object, module or entity. Ports are normally attached to I/O pads and connect externally to the FPGA device.

#### Net

A net is a wire or list of wires that eventually be physically connected directly together. Nets can be hierarchical or flat, but always sorts a list of pins together.

#### Clock

A clock is a periodic signal that propagates to sequential logic within a design. Clocks can be primary clock domains or generated by clock primitives such as a DCM, PLL, or MMCM. A clock is the rough equivalent to a TIMESPEC PERIOD constraint in UCF and forms the basis of static timing analysis algorithms.

## **Querying Objects**

All first class objects can be queried by a get\_ Tcl command that generally has the following syntax:

```

get object type pattern

```

Where pattern is a search pattern, which includes if applicable a hierarchy separator to get a fully qualified name. Objects are generally queried by a string pattern match applied at each level of the hierarchy, and the search pattern also supports wildcard style search patterns to make it easier to find objects, for example:

```

get cells */inst 1

```

This command searches for a cell named inst\_1 within the first level of hierarchy under the top-level of hierarchy. To recursively search for a pattern at every level of hierarchy, use the following syntax:

```

get cells -hierarchical inst 1

```

This command searches every level of hierarchy for any instances that match inst\_1.

For complete coverage of the command syntax, see the specific online help for the individual command:

- help get cells

- get cells -help

#### **Object Properties**

Objects have properties that can be queried. Property names are unique for any given object type. To query a specific property for an object, the following command is provided:

```

get property property name object

```

For example, the lib\_cell property on cell objects tells you what UniSim component a given instance is mapped to:

```

get property lib cell [get cell inst 1]

```

To discover all of the available properties for a given object type, use the <code>report\_property</code> command:

```

report property [get cells inst 1]

```

The following table shows the properties returned for a specific object.

| Кеу                | Value          | Туре   |

|--------------------|----------------|--------|

| bel                | OLOGICE1.OUTFF | string |

| class              | cell           | string |

| iob                | TRUE           | string |

| is_blackbox        | 0              | bool   |

| is_fixed           | 0              | bool   |

| is_partition       | 0              | bool   |

| is_primitive       | 1              | bool   |

| is_reconfigurable  | 0              | bool   |

| is_sequential      | 1              | bool   |

| lib_cell           | FD             | string |

| loc                | OLOGIC_X1Y27   | string |

| name               | error          | string |

| primitive_group    | FD_LD          | string |

| primitive_subgroup | flop           | string |

| site               | OLOGIC_X1Y27   | string |

| type               | FD & LD        | string |

| XSTLIB             | 1              | bool   |

Some properties are read-only and some are user-settable. Properties that map to attributes that can be annotated in UCF or in HDL are generally user-settable through Tcl with the set\_property command:

```

set property loc OLOGIC X1Y27 [get cell inst 1]

```

## **Filtering Based on Properties**

The object query get\_\* commands have a common option to filter the query based on any property value attached to the object. This is a powerful capability for the object query commands. For example, to query all cells of primitive type FD do the following:

```

get cells * -hierarchical -filter "lib cell == FD"

```

To do more elaborate string filtering, utilize the =~ operator to do string pattern matching. For example, to query all flip-flop types in the design, do the following:

```

get cells * -hierarchical -filter "lib cell =~ FD*"

```

Multiple filter properties can be combined with other property filters with logical OR (||) and AND (&&) operators to make very powerful searches. To query every cell in the design that if of any flop type and has a placed location constraint:

```

get cells * -hierarchical -filter {lib cell =~ FD* && loc != ""}

```

**NOTE:** In the example, the filter option value was wrapped with curly braces {} instead of double quotes. This is normal Tcl syntax that prevents command substitution by the interpreter and allows users to pass the empty string ("") to the loc property.

#### **Handling Lists of Objects**

Commands that return more than one object, such as <code>get\_cells</code> or <code>get\_sites</code>, return a collection in the Vivado tool that looks and behaves like a native Tcl list. This feature allows performance gains when handling large lists of Tcl objects without the need to use special commands like the foreach\_in\_collection command. In the Vivado Design Suite collections can be processed like Tcl lists using built-in commands such as lsort, lsearch, and foreach.

Typically, when you run a <code>get\_\*</code> command, the returned results are echoed to the console and to the log file as a Tcl string, rather than as a list due to a feature of Tcl called "shimmering". Internally, Tcl can store a variable or value both as a string and as a faster native object such as a float or a list object. In Tcl, shimmering occurs when the representation of the object or value changes from the list object to the string object, or from string to list. A list of Vivado objects is returned by the <code>get\_\*</code> command, but the shimmered string representation is written to the log file and Tcl console.

However, to improve performance and prevent overloading memory buffers, the Vivado Design Suite limits and truncates the shimmered string to a default character length defined by the tcl.collectionResultDisplayLimit parameter, which has a default value of 500. Commands that can return a significant number of objects, such as get\_cells or get\_sites, will truncate the returned string, ending it with an ellipsis ('...'). You can use the set\_param command to change the tcl.collectionResultDisplayLimit parameter value to return more or fewer results.

**CAUTION!** The combination of shimmering and the tcl.collectionResultDisplayLimit parameter prevents the use of in and ni list operators in the Vivado Design Suite. Since a string shimmered from the list may be truncated, the in and ni operators cannot effectively determine if a specified object is in, or not-in, a list of objects. You should use list commands such as lsearch and lsort instead of in or ni.

```

if {[lsearch -exact [get cells *] $cellName] != -1} {...}

```

You can capture the complete list returned by the get\_\* command by assigning the results to a Tcl variable:

```

set allSites [get_sites]

```

The actual list in the variable assignment includes the complete result set, and is not truncated by the tcl.collectionResultDisplayLimit parameter. An example of this is seen in hierarchically querying all the cells in a design:

```

%set allCells [get_cells -hierarchical]

DataIn_pad_0_i_IBUF[0]_inst DataIn_pad_0_i_IBUF[1]_inst \

DataIn_pad_0_i_IBUF[2]_inst DataIn_pad_0_i_IBUF[3]_inst \

DataIn_pad_0_i_IBUF[4]_inst ...

%llength $allCells

42244

%lindex $allCells end

wbArbEngine/s4/next reg

```

In the preceding example, the result of the hierarchical <code>get\_cells</code> command was assigned to the <code>\$allCells</code> variable. In appearance, the results are truncated. However, a check of the length of the list reports more than forty thousand cell objects, and the last index in the list returns an actual object, and not an ellipsis.

**TIP:** If necessary, you can also use the join command, to join the list of objects returned by the get \* Tcl command, with a newline (\n), tab (\t), or a space (" "), to display the un-truncated list of objects:

```

join [get_parts] " "

```

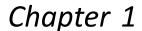

## **Object Relationships**

Related objects can be queried using the -of option to the relevant get\_\* command. For example, to get a list of pins connected to a cell object, do the following:

```

get pins -of [get cells inst 1]

```

The following image shows object types in the Vivado tool and their relationships, where an arrow from one object to another object indicates that you can use the <code>-of</code> option to the <code>get\_\*</code> command to traverse logical connectivity and get Tcl references to any connected object. For more information on first class objects and their relationships, refer to the *Vivado Design Suite Properties Reference Guide (UG912)*.

# Errors, Warnings, Critical Warnings, and Info Messages

Messages that result from individual commands appear in the log file as well as in the GUI console if it is active. These messages are generally numbered to identify specific issues and are prefixed in the log file with "INFO", "WARNING", "CRITICAL\_Warning", "ERROR" followed by a subsystem identifier and a unique number.

The following example shows an INFO message that appears after reading the timing library.

INFO: [HD-LIB 1] Done reading timing library

These messages make it easier to search for specific issues in the log file to help to understand the context of operations during command execution.

Generally, when an error occurs in a Tcl command sourced from a Tcl script, further execution of subsequent commands is halted. This is to prevent unrecoverable error conditions. There are Tcl built-ins that allow users to intercept these error conditions, and to choose to continue. Consult any Tcl reference for the catch command for a description of how to handle errors using general Tcl mechanisms.

# Tcl Commands Listed by Category

## **Categories**

- Bitgen

- Board

- CreatePeripheral

- DRC

- Debug

- FileIO

- Floorplan

- GUIControl

- Hardware

- IPFlow

- IPIntegrator

- Memory

- Methodology

- Netlist

- Object

- Partition

- PinPlanning

- Power

- Project

- PropertyAndParameter

- Report

- SDC

- Simulation

- SysGen

- Tcl

- Timing

- ToolLaunch

- Tools

- Waveform

- XDC

- XPS

- projutils

- simulation

- synthesis

- user-written

- xilinxtclstore

# Bitgen:

calc\_config\_time

### **Board:**

- apply\_board\_connection

- current\_board

- current\_board\_part

- get\_board\_bus\_nets

- get\_board\_buses

- get\_board\_component\_interfaces

- get\_board\_component\_modes

- get\_board\_component\_pins

- get\_board\_components

- get\_board\_interface\_ports

- get\_board\_ip\_preferences

- get\_board\_jumpers

- get\_board\_parameters

- get\_board\_part\_interfaces

- get\_board\_part\_pins

- get\_board\_parts

- get\_boards

# **CreatePeripheral:**

- add\_peripheral\_interface

- create\_peripheral

- generate\_peripheral

- write\_peripheral

### **DRC**:

- add\_drc\_checks

- create\_drc\_check

- create\_drc\_ruledeck

- create\_drc\_violation

- delete\_drc\_check

- delete\_drc\_ruledeck

- get\_drc\_checks

- get\_drc\_ruledecks

- get\_drc\_violations

- remove\_drc\_checks

- report\_drc

- reset\_drc

- reset\_drc\_check

# Debug:

- apply\_hw\_ila\_trigger

- connect\_debug\_port

- create\_debug\_core

- create\_debug\_port

- delete\_debug\_core

- delete\_debug\_port

- disconnect\_debug\_port

- get\_debug\_cores

- get\_debug\_ports

- implement\_debug\_core

- report\_debug\_core

- write\_debug\_probes

## FileIO:

- auto\_detect\_xpm

- config\_webtalk

- decrypt\_bitstream

- encrypt

- generate\_mem\_files

- infer\_diff\_pairs

- pr\_verify

- read\_bd

- read\_checkpoint

- read\_csv

- read\_edif

- read\_ip

- read\_mem

- read\_saif

- read\_schematic

- read\_twx

- read\_verilog

- read\_vhdl

- read\_xdc

- write\_bd\_layout

- write\_bitstream

- write\_bmm

- write\_bsdl

- write\_cfgmem

- write\_checkpoint

- write\_csv

- write\_debug\_probes

- write\_edif

- write\_ibis

- write\_inferred\_xdc

- write\_mem\_info

- write\_schematic

- write\_sdf

- write\_verilog

- write\_vhdl

- write\_xdc

# Floorplan:

- add\_cells\_to\_pblock

- create\_pblock

- delete\_pblocks

- delete\_rpm

- get\_pblocks

- place\_cell

- place\_pblocks

- remove\_cells\_from\_pblock

- resize\_pblock

- swap\_locs

- unplace\_cell

## **GUIControl:**

- endgroup

- get\_highlighted\_objects

- get\_marked\_objects

- get\_selected\_objects

- highlight\_objects

- mark\_objects

- redo

- select\_objects

- show\_objects

- show\_schematic

- start\_gui

- startgroup

- stop\_gui

- undo

- unhighlight\_objects

- unmark\_objects

- unselect\_objects

## Hardware:

add\_hw\_probe\_enum

- boot\_hw\_device

- close\_hw

- close\_hw\_target

- commit\_hw\_mig

- commit\_hw\_sio

- commit\_hw\_sysmon

- commit\_hw\_vio

- config\_hw\_sio\_gts

- connect\_hw\_server

- create\_hw\_axi\_txn

- create\_hw\_bitstream

- create\_hw\_cfgmem

- create\_hw\_device

- create\_hw\_probe

- create\_hw\_sio\_link

- create\_hw\_sio\_linkgroup

- create\_hw\_sio\_scan

- create\_hw\_sio\_sweep

- create\_hw\_target

- current\_hw\_cfgmem

- current\_hw\_device

- current\_hw\_ila

- current\_hw\_ila\_data

- current hw server

- current\_hw\_target

- delete\_hw\_axi\_txn

- delete\_hw\_bitstream

- delete\_hw\_cfgmem

- delete\_hw\_probe

- delete\_hw\_target

- detect\_hw\_sio\_links

- disconnect\_hw\_server

- display\_hw\_ila\_data

- display\_hw\_sio\_scan

- execute\_hw\_svf

- get\_cfgmem\_parts

- get\_hw\_axi\_txns

- get\_hw\_axis

- get\_hw\_cfgmems

- get\_hw\_devices

- get\_hw\_ila\_datas

- get\_hw\_ilas

- get\_hw\_migs

- get\_hw\_probes

- get\_hw\_servers

- get\_hw\_sio\_commons

- get\_hw\_sio\_gtgroups

- get\_hw\_sio\_gts

- get\_hw\_sio\_iberts

- get\_hw\_sio\_linkgroups

- get\_hw\_sio\_links

- get\_hw\_sio\_plls

- get\_hw\_sio\_rxs

- get\_hw\_sio\_scans

- get\_hw\_sio\_sweeps

- get\_hw\_sio\_txs

- get\_hw\_sysmon\_reg

- get\_hw\_sysmons

- get\_hw\_targets

- get\_hw\_vios

- list\_hw\_samples

- open\_hw

- open\_hw\_target

- program\_hw\_cfgmem

- program\_hw\_devices

- read\_hw\_ila\_data

- read\_hw\_sio\_scan

- read\_hw\_sio\_sweep

- readback\_hw\_cfgmem

- readback\_hw\_device

- refresh\_hw\_axi

- refresh\_hw\_device

- refresh\_hw\_mig

- refresh\_hw\_server

- refresh\_hw\_sio

- refresh\_hw\_sysmon

- refresh\_hw\_target

- refresh\_hw\_vio

- remove\_hw\_probe\_enum

- remove\_hw\_sio\_link

- remove\_hw\_sio\_linkgroup

- remove\_hw\_sio\_scan

- remove\_hw\_sio\_sweep

- report\_hw\_axi\_txn

- report\_hw\_mig

- report\_hw\_targets

- reset\_hw\_axi

- reset\_hw\_ila

- reset\_hw\_vio\_activity

- reset\_hw\_vio\_outputs

- run\_hw\_axi

- run\_hw\_ila

- run\_hw\_sio\_scan

- run\_hw\_sio\_sweep

- run\_state\_hw\_jtag

- runtest\_hw\_jtag

- scan\_dr\_hw\_jtag

- scan\_ir\_hw\_jtag

- set\_hw\_sysmon\_reg

- stop\_hw\_sio\_scan

- stop\_hw\_sio\_sweep

- update\_smartcable

- upload\_hw\_ila\_data

- verify\_hw\_devices

- wait\_on\_hw\_ila

- wait\_on\_hw\_sio\_scan

- wait\_on\_hw\_sio\_sweep

- write\_hw\_ila\_data

- write\_hw\_sio\_scan

- write\_hw\_sio\_sweep

- write\_hw\_svf

## **IPFlow:**

- add\_peripheral\_interface

- compile\_c

- config\_ip\_cache

- convert\_ips

- copy\_ip

- create\_ip

- create\_ip\_run

- create\_peripheral

- delete\_ip\_run

- extract\_files

- generate\_peripheral

- generate\_target

- get\_ip\_upgrade\_results

- get\_ipdefs

- get\_ips

- import\_ip

- open\_example\_project

- read\_ip

- report\_ip\_status

- reset\_target

- synth\_ip

- update\_ip\_catalog

- update\_module\_reference

- upgrade\_ip

- validate\_ip

- write\_peripheral

## **IPIntegrator:**

- apply\_bd\_automation

- apply\_board\_connection

- assign\_bd\_address

- close\_bd\_design

- compile\_c

- connect\_bd\_intf\_net

- connect\_bd\_net

- copy\_bd\_objs

- create\_bd\_addr\_seg

- create\_bd\_cell

- create\_bd\_design

- create\_bd\_intf\_net

- create\_bd\_intf\_pin

- create\_bd\_intf\_port

- create\_bd\_net

- create\_bd\_pin

- create\_bd\_port

- current\_bd\_design

- current\_bd\_instance

- delete\_bd\_objs

- disconnect\_bd\_intf\_net

- disconnect\_bd\_net

- exclude\_bd\_addr\_seg

- find\_bd\_objs

- generate\_target

- get\_bd\_addr\_segs

- get\_bd\_addr\_spaces

- get\_bd\_cells

- get\_bd\_designs

- get\_bd\_intf\_nets

- get\_bd\_intf\_pins

- get\_bd\_intf\_ports

- get\_bd\_nets

- get\_bd\_pins

- get\_bd\_ports

- get\_example\_designs

- get\_template\_bd\_designs

- group\_bd\_cells

- include\_bd\_addr\_seg

- instantiate\_example\_design

- instantiate\_template\_bd\_design

- make\_bd\_intf\_pins\_external

- make\_bd\_pins\_external

- move\_bd\_cells

- open\_bd\_design

- read bd

- regenerate\_bd\_layout

- replace\_bd\_cell

- save\_bd\_design

- ungroup\_bd\_cells

- upgrade\_bd\_cells

- validate\_bd\_design

- write\_bd\_tcl

## **Memory:**

implement\_mig\_cores

# Methodology:

- get\_methodology\_checks

- get\_methodology\_violations

- report\_methodology

## **Netlist:**

- connect\_net

- create\_cell

- create\_net

- create\_pin

- disconnect\_net

- get\_net\_delays

- remove\_cell

- remove\_net

- remove\_pin

- rename\_cell

- rename\_net

- rename\_pin

- rename\_port

- rename\_ref

- resize\_net\_bus

- resize\_pin\_bus

- tie\_unused\_pins

## **Object:**

- add\_drc\_checks

- apply\_board\_connection

- config\_ip\_cache

- create\_drc\_check

- create\_drc\_ruledeck

- create\_partition\_def

- create\_pr\_configuration

- create\_reconfig\_module

- current\_board

- current\_board\_part

- current\_pr\_configuration

- delete\_drc\_check

- delete\_drc\_ruledeck

- delete\_hw\_bitstream

- filter

- find\_routing\_path

- get\_bel\_pins

- get\_bels

- get\_board\_bus\_nets

- get\_board\_buses

- get\_board\_component\_interfaces

- get\_board\_component\_modes

- get\_board\_component\_pins

- get\_board\_components

- get\_board\_interface\_ports

- get\_board\_ip\_preferences

- get\_board\_jumpers

- get\_board\_parameters

- get\_board\_part\_interfaces

- get\_board\_part\_pins

- get\_board\_parts

- get\_boards

- get\_cells

- get\_cfgmem\_parts

- get\_clock\_regions

- get\_clocks

- get\_debug\_cores

- get\_debug\_ports

- get\_designs

- get\_drc\_checks

- get\_drc\_ruledecks

- get\_drc\_violations

- get\_files

- get\_filesets

- get\_generated\_clocks

- get\_highlighted\_objects

- get\_hw\_axi\_txns

- get\_hw\_axis

- get\_hw\_cfgmems

- get\_hw\_devices

- get\_hw\_ila\_datas

- get\_hw\_ilas

- get\_hw\_migs

- get\_hw\_probes

- get\_hw\_servers

- get\_hw\_sio\_commons

- get\_hw\_sio\_gtgroups

- get\_hw\_sio\_gts

- get\_hw\_sio\_iberts

- get\_hw\_sio\_linkgroups

- get\_hw\_sio\_links

- get\_hw\_sio\_plls

- get\_hw\_sio\_rxs

- get\_hw\_sio\_scans

- get\_hw\_sio\_sweeps

- get\_hw\_sio\_txs

- get\_hw\_sysmons

- get\_hw\_targets

- get\_hw\_vios

- get\_interfaces

- get\_io\_standards

- get\_iobanks

- get\_ip\_upgrade\_results

- get\_ipdefs

- get\_ips

- get\_lib\_cells

- get\_lib\_pins

- get\_libs

- get\_macros

- get\_marked\_objects

- get\_methodology\_checks

- get\_methodology\_violations

- get\_net\_delays

- get\_nets

- get\_nodes

- get\_package\_pins

- get\_partition\_defs

- get\_parts

- get\_path\_groups

- get\_pblocks

- get\_pins

- get\_pips

- get\_pkgpin\_bytegroups

- get\_pkgpin\_nibbles

- get\_ports

- get\_pr\_configurations

- get\_primitives

- get\_projects

- get\_property

- get\_reconfig\_modules

- get\_runs

- get\_selected\_objects

- get\_site\_pins

- get\_site\_pips

- get\_sites

- get\_slrs

- get\_speed\_models

- get\_tiles

- get\_timing\_arcs

- get\_timing\_paths

- get\_wires

- list\_hw\_samples

- list\_property

- list\_property\_value

- remove\_drc\_checks

- report\_property

- reset\_drc\_check

- reset\_property

- run\_state\_hw\_jtag

- runtest\_hw\_jtag

- scan\_dr\_hw\_jtag

- scan\_ir\_hw\_jtag

- set\_property

### **Partition:**

- create\_partition\_def

- create\_pr\_configuration

- create\_reconfig\_module

- current\_pr\_configuration

- delete\_partition\_defs

- delete\_pr\_configurations

- delete\_reconfig\_modules

- get\_partition\_defs

- get\_pr\_configurations

- get\_reconfig\_modules

- setup\_pr\_configurations

# **PinPlanning:**

- create\_interface

- create\_port

- delete\_interface

- make\_diff\_pair\_ports

- place\_ports

- remove\_port

- resize\_port\_bus

- set\_package\_pin\_val

- split\_diff\_pair\_ports

#### **Power:**

- delete\_power\_results

- power\_opt\_design

- read\_saif

- report\_power

- report\_power\_opt

- reset\_operating\_conditions

- reset\_switching\_activity

- set\_operating\_conditions

- set\_power\_opt

- set\_switching\_activity

# **Project:**

- add files

- add\_peripheral\_interface

- apply\_board\_connection

- archive\_project

- auto\_detect\_xpm

- check\_syntax

- close\_design

- close\_project

- compile\_c

- copy\_ip

- create\_fileset

- create\_ip\_run

- create\_peripheral

- create\_project

- create\_run

- create\_xps

- current\_board\_part

- current\_fileset

- current\_project

- current\_run

- delete\_fileset

- delete\_ip\_run

- delete\_runs

- find\_top

- generate\_peripheral

- generate\_target

- get\_board\_parts

- get\_boards

- get\_files

- get\_filesets

- get\_ip\_upgrade\_results

- get\_ips

- get\_projects

- get\_runs

- help

- import\_files

- import\_ip

- import\_synplify

- import\_xise

- import\_xst

- launch\_runs

- list\_targets

- lock\_design

- make\_wrapper

- move\_files

- open\_checkpoint

- open\_example\_project

- open\_io\_design

- open\_project

- open\_run

- refresh\_design

- reimport\_files

- remove\_files

- reorder\_files

- report\_compile\_order

- reset\_project

- reset\_run

- reset\_target

- save\_constraints

- save\_constraints\_as

- save\_project\_as

- set\_part

- set\_speed\_grade

- synth\_ip

- update\_compile\_order

- update\_design

- update\_files

- validate\_dsa

- wait\_on\_run

- write\_hwdef

- write\_peripheral

- write\_sysdef

## **PropertyAndParameter:**

- create\_property

- filter

- get\_param

- get\_property

- list\_param

- list\_property

- list\_property\_value

- report\_param

- report\_property

- reset\_param

- reset\_property

- set\_param

- set\_part

- set\_property

## Report:

- calc\_config\_time

- check\_timing

- create\_drc\_violation

- create\_slack\_histogram

- delete\_clock\_networks\_results

- delete\_timing\_results

- delete\_utilization\_results

- get\_msg\_config

- get\_pplocs

- open\_report

- report\_bus\_skew

- report\_carry\_chains

- report\_cdc

- report\_clock\_interaction

- report\_clock\_networks

- report\_clock\_utilization

- report\_clocks

- report\_config\_timing

- report\_control\_sets

- report\_datasheet

- report\_debug\_core

- report\_design\_analysis

- report\_disable\_timing

- report\_drc

- report\_environment

- report\_exceptions

- report\_high\_fanout\_nets

- report\_hw\_mig

- report\_incremental\_reuse

- report\_io

- report\_methodology

- report\_operating\_conditions

- report\_param

- report\_phys\_opt

- report\_power

- report\_pr\_configuration\_analysis

- report\_property

- report\_pulse\_width

- report\_qor\_suggestions

- report\_ram\_utilization

- report\_route\_status

- report\_sim\_device

- report\_ssn

- report\_switching\_activity

- report\_synchronizer\_mtbf

- report\_timing

- report\_timing\_summary

- report\_transformed\_primitives

- report\_utilization

- reset\_drc

- reset\_msg\_config

- reset\_msg\_count

- reset\_ssn

- reset\_timing

- set\_msg\_config

- version

### SDC:

- all\_clocks

- all\_inputs

- all\_outputs

- all\_registers

- create\_clock

- create\_generated\_clock

- current\_design

- current\_instance

- get\_cells

- get\_clocks

- get\_hierarchy\_separator

- get\_nets

- get\_pins

- get\_ports

- group\_path

- set\_case\_analysis

- set\_clock\_groups

- set\_clock\_latency

- set\_clock\_sense

- set\_clock\_uncertainty

- set\_data\_check

- set\_disable\_timing

- set\_false\_path

- set\_hierarchy\_separator

- set\_input\_delay

- set\_load

- set\_logic\_dc

- set\_logic\_one

- set\_logic\_zero

- set\_max\_delay

- set\_max\_time\_borrow

- set\_min\_delay

- set\_multicycle\_path

- set\_operating\_conditions

- set\_output\_delay

- set\_propagated\_clock

- set\_units

### **Simulation:**

- add\_bp

- add\_condition

- add\_files

- add\_force

- checkpoint\_vcd

- close\_saif

- close\_sim

- close\_vcd

- compile\_simlib

- config\_compile\_simlib

- create\_fileset

- current\_scope

- current\_sim

- current\_time

- current\_vcd

- delete\_fileset

- describe

- export\_ip\_user\_files

- export\_simulation

- flush\_vcd

- generate\_mem\_files

- get\_objects

- get\_scopes

- get\_simulators

- get\_value

- import\_files

- launch\_simulation

- limit\_vcd

- log\_saif

- log\_vcd

- log\_wave

- Itrace

- move\_files

- open\_saif

- open\_vcd

- open\_wave\_database

- ptrace

- read\_saif

- relaunch\_sim

- remove\_bps

- remove\_conditions

- remove\_files

- remove\_forces

- report\_bps

- report\_conditions

- report\_drivers

- report\_objects

- report\_scopes

- report\_simlib\_info

- report\_values

- reset\_simulation

- restart

- run

- set\_value

- setup\_ip\_static\_library

- start\_vcd

- step

- stop

- stop\_vcd

- write\_sdf

- write\_verilog

- write\_vhdl

- xsim

# SysGen:

- create\_sysgen

- make\_wrapper

## Tcl:

- report\_pipeline\_analysis

- update\_clock\_routing

# Timing:

- check\_timing

- config\_design\_analysis

- config\_timing\_analysis

- config\_timing\_corners

- create\_slack\_histogram

- delete\_timing\_results

- get\_net\_delays

- get\_timing\_arcs

- get\_timing\_paths

- report\_bus\_skew

- report\_cdc

- report\_clock\_interaction

- report\_clock\_networks

- report\_clock\_utilization

- report\_clocks

- report\_config\_timing

- report\_datasheet

- report\_design\_analysis

- report\_disable\_timing

- report\_drc

- report\_exceptions

- report\_high\_fanout\_nets

- report\_methodology

- report\_pulse\_width

- report\_qor\_suggestions

- report\_synchronizer\_mtbf

- report\_timing

- report\_timing\_summary

- reset\_timing

- set\_delay\_model

- set\_disable\_timing

- set\_external\_delay

- update\_timing

- write\_inferred\_xdc

- write\_sdf

- write\_xdc

### **ToolLaunch:**

- get\_simulators

- launch\_chipscope\_analyzer

- launch\_impact

- launch\_sdk

- launch\_simulation

### **Tools:**

- iphys\_opt\_design

- link\_design

- list\_features

- load\_features

- opt\_design

- phys\_opt\_design

- place\_design

- read\_iphys\_opt\_tcl

- register\_proc

- report\_pipeline\_analysis

- route\_design

- synth\_design

- unregister\_proc

- update\_clock\_routing

- write\_iphys\_opt\_tcl

### Waveform:

- add\_wave

- add\_wave\_divider

- add\_wave\_group

- add\_wave\_marker

- add\_wave\_virtual\_bus

- close\_wave\_config

- create\_wave\_config

- current\_wave\_config

- get\_wave\_configs

- get\_waves

- move\_wave

- open\_wave\_config

- remove\_wave

- save\_wave\_config

- select\_wave\_objects

### **XDC:**

- add\_cells\_to\_pblock

- all\_clocks

- all\_cpus

- all\_dsps

- all\_fanin

- all\_fanout

- all\_ffs

- all\_hsios

- all\_inputs

- all\_latches

- all\_outputs

- all\_rams

- all\_registers

- connect\_debug\_port

- create\_clock

- create\_debug\_core

- create\_debug\_port

- create\_generated\_clock

- create\_macro

- create\_pblock

- create\_property

- current\_design

- current\_instance

- delete\_macros

- delete\_pblocks

- filter

- get\_bel\_pins

- get\_bels

- get\_cells

- get\_clocks

- get\_debug\_cores

- get\_debug\_ports

- get\_generated\_clocks

- get\_hierarchy\_separator

- get\_iobanks

- get\_macros

- get\_nets

- get\_nodes

- get\_package\_pins

- get\_path\_groups

- get\_pblocks

- get\_pins

- get\_pips

- get\_pkgpin\_bytegroups

- get\_pkgpin\_nibbles

- get\_ports

- get\_property

- get\_site\_pins

- get\_site\_pips

- get\_sites

- get\_slrs

- get\_speed\_models

- get\_tiles

- get\_timing\_arcs

- get\_wires

- group\_path

- make\_diff\_pair\_ports

- remove\_cells\_from\_pblock

- reset\_operating\_conditions

- reset\_switching\_activity

- resize\_pblock

- set\_bus\_skew

- set\_case\_analysis

- set\_clock\_groups

- set\_clock\_latency

- set\_clock\_sense

- set\_clock\_uncertainty

- set\_data\_check

- set\_disable\_timing

- set\_external\_delay

- set\_false\_path

- set\_hierarchy\_separator

- set\_input\_delay

- set\_input\_jitter

- set\_load

- set\_logic\_dc

- set\_logic\_one

- set\_logic\_unconnected

- set\_logic\_zero

- set\_max\_delay

- set\_max\_time\_borrow

- set\_min\_delay

- set\_multicycle\_path

- set\_operating\_conditions

- set\_output\_delay

- set\_package\_pin\_val

- set\_power\_opt

- set\_propagated\_clock

- set\_property

- set\_switching\_activity

- set\_system\_jitter

- set\_units

- update\_macro

### XPS:

get\_board\_parts

# projutils:

- convert\_ngc

- copy\_run

- export\_bd\_synth

- write\_project\_tcl

# simulation:

- add\_bp

- add\_condition

- add\_files

- add\_force

- checkpoint\_vcd

- close\_saif

- close\_sim

- close\_vcd

- compile\_simlib

- config\_compile\_simlib

- create\_fileset

- current\_scope

- current\_sim

- current\_time

- current\_vcd

- delete\_fileset

- describe

- export\_ip\_user\_files

- export\_simulation

- flush\_vcd

- generate\_mem\_files

- get\_objects

- get\_scopes

- get\_simulators

- get\_value

- import\_files

- launch\_simulation

- limit\_vcd

- log\_saif

- log\_vcd

- log\_wave

- Itrace

- move\_files

- open\_saif

- open\_vcd

- open\_wave\_database

- ptrace

- read\_saif

- relaunch\_sim

- remove\_bps

- remove\_conditions

- remove\_files

- remove\_forces

- report\_bps

- report\_conditions

- report\_drivers

- report\_objects

- report\_scopes

- report\_simlib\_info

- report\_values

- reset\_simulation

- restart

- run

- set\_value

- setup\_ip\_static\_library

- start\_vcd

- step

- stop

- stop\_vcd

- write\_sdf

- write\_verilog

- write\_vhdl

- xsim

# synthesis:

export\_bd\_synth

### user-written:

- convert\_ngc

- copy\_run

- export\_bd\_synth

- export\_ip\_user\_files

- export\_simulation

- setup\_ip\_static\_library

- write\_project\_tcl

# xilinxtclstore:

- convert\_ngc

- copy\_run

- export\_bd\_synth

- export\_ip\_user\_files

- export\_simulation

- setup\_ip\_static\_library

- write\_project\_tcl

# Tcl Commands Listed Alphabetically

This chapter contains all SDC and Tcl commands, arranged alphabetically.

## add bp

Add breakpoint at a line of a HDL source.

### **Syntax**

add\_bp [-quiet] [-verbose] <file\_name> <line\_number>

#### Returns

Return a new breakpoint object if there is not already a breakpoint set at the specified file line else returns the existing breakpoint object

### **Usage**

| Name                                   | Description                                         |

|----------------------------------------|-----------------------------------------------------|

| [-quiet]                               | Ignore command errors                               |

| [-verbose]                             | Suspend message limits during command execution     |

| <file_name></file_name>                | Filename to add the breakpoint                      |

| <pre><line_number></line_number></pre> | Line number of the given file to set the breakpoint |

### **Categories**

Simulation

### **Description**

The add\_bp command lets you add breakpoints to an HDL source file to pause the current simulation.

A breakpoint is a user-determined stopping point in the source code used for debugging the design. When simulating a design with breakpoints, simulation of the design stops at each breakpoint to let you examine values and verify the design behavior.

You can report breakpoints in the current simulation using the report\_bps command, and remove existing breakpoints using the remove\_bps command.

This command returns a new breakpoint object if there is not already a breakpoint set at the specified file line, or returns an existing breakpoint object if there is already a breakpoint defined for the specified file and line number.

**TIP:** You can capture the returned breakpoint object in a Tcl variable if needed.

The add bp command returns an error if the command fails.

### **Arguments**

-quiet - (Optional) Execute the command quietly, returning no messages from the command. The command also returns TCL\_OK regardless of any errors encountered during execution.

**NOTE:** Any errors encountered on the command-line, while launching the command, will be returned. Only errors occurring inside the command will be trapped.

-verbose - (Optional) Temporarily override any message limits and return all messages from this command.

**NOTE:** Message limits can be defined with the set\_msg\_config command.

<file name> - (Required) The name of the HDL source file to add a breakpoint to.

<line\_number> - (Required) The line number of the specified <file\_name> to add the breakpoint to.

### **Examples**

The following example adds a the breakpoint to the HDL source file at the specified line number:

add bp C:/Data/ug937/sources/sinegen.vhd 137

- remove\_bps

- report\_bps

# add\_cells\_to\_pblock

Add cells to a Pblock.

### **Syntax**

add\_cells\_to\_pblock [-top] [-add\_primitives] [-clear\_locs] [-quiet]

[-verbose] <pblock> [<cells>...]

#### Returns

**Nothing**

### **Usage**

| Name               | Description                                                                                                                                   |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [-top]             | Add the top level instance; This option can't be used with -cells, or -add_primitives options. You must specify either -cells or -top option. |

| [-add_primitives]  | Assign to the pblock only primitive cells from the specified list of cells.                                                                   |

| [-clear_locs]      | Clear instance location constraints                                                                                                           |

| [-quiet]           | Ignore command errors                                                                                                                         |

| [-verbose]         | Suspend message limits during command execution                                                                                               |

| <pblock></pblock>  | Pblock to add cells to                                                                                                                        |

| [ <cells>]</cells> | Cells to add. You can't use this option with -top option. You must specify either -cells or -top option.                                      |

### **Categories**

Floorplan, XDC

### **Description**

Adds specified logic instances to a Pblock in an open implemented design. Once cells have been added to a Pblock, you can place the Pblocks onto the fabric of the FPGA using the resize\_pblock command. The resize\_pblock command can also be used to manually move and resize Pblocks.

You can remove instances from the Pblock using the remove cells from pblock command.

### **Arguments**

-top - (Optional) Add the top level instance to create a Pblock for the whole design. You must either specify <cells> or the -top option to add objects to the Pblock.

-add\_primitives - (Optional) Assign all primitives of the specified instances to a Pblock. This lets you select all cells in a hierarchical module, and assign only the leaf-cells of the selected cells to the specified Pblock.

**NOTE:** This option cannot be used with -top.

-clear locs - (Optional) Clear instance location constraints for any cells that are already placed. This allows you to reset the LOC constraint for cells when defining new Pblocks for floorplanning purposes. When this option is not specified, any instances with assigned placement will not be unplaced as they are added to the Pblock.

-quiet - (Optional) Execute the command quietly, returning no messages from the command. The command also returns TCL\_OK regardless of any errors encountered during execution.

**NOTE:** Any errors encountered on the command-line, while launching the command, will be returned. Only errors occurring inside the command will be trapped.

-verbose - (Optional) Temporarily override any message limits and return all messages from this command.

**NOTE:** Message limits can be defined with the set msg config command.

<pblock> - The name assigned to the Pblock.

<cells> - One or more cell objects to add to the specified Pblock.

**NOTE:** If -top is specified, you cannot also specify <cells>.

### **Examples**

The following example creates a Pblock called pb\_cpuEngine, and then adds only the leaf-cells found in the cpuEngine module, clearing placement constraints for placed instances:

```

create_pblock pb_cpuEngine

add_cells_to_pblock pb_cpuEngine [get_cells cpuEngine/*] \

-add primitives -clear locs

```

- get\_pblocks

- place\_pblocks

- remove\_cells\_from\_pblock

- resize\_pblock

# add\_condition

Conditionally execute Tcl commands.

### **Syntax**

add\_condition [-name <arg>] [-radix <arg>] [-quiet] [-verbose]

<condition expression> <commands>

#### **Returns**

The condition object created

### **Usage**

| Name                                                     | Description                                                                                                                                                                                            |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [-name]                                                  | Assign a unique name (label) to a condition. Multiple conditions cannot be assigned the same name. If no name is specified, then a default label named as condition <id> is automatically created</id> |

| [-radix]                                                 | Specifies which radix to use. Allowed values are: default, dec, bin, oct, hex, unsigned, ascii, smag.                                                                                                  |

| [-quiet]                                                 | Ignore command errors                                                                                                                                                                                  |

| [-verbose]                                               | Suspend message limits during command execution                                                                                                                                                        |

| <pre><condition_expression></condition_expression></pre> | The condition expression when true executes the given commands                                                                                                                                         |

| <commands></commands>                                    | Commands to execute upon condition                                                                                                                                                                     |

## **Categories**

Simulation

### **Description**

Add a condition that is evaluated by a specified condition, condition\_expression, and runs a series of simulation Tcl commands when the condition is TRUE.

Conditions can be defined prior to starting the simulation. When a condition is added, the simulator evaluates the condition expression anytime a signal change is detected. When a specified condition expression becomes TRUE, the condition commands are run.

The add\_condition command returns a condition identifier for the added condition, or returns an error if the command fails.

### **Arguments**

-name <arg> - (Optional) Provide a unique name for the condition. If no name is specified, then a default named is automatically created.

-radix <arg> - (Optional) Specifies the radix to use for the value of the condition. Allowed values are: default, dec, bin , oct, hex, unsigned , and ascii.

**NOTE:** The radix dec indicates a signed decimal. Specify the radix unsigned when dealing with unsigned data.

-quiet - (Optional) Execute the command quietly, returning no messages from the command. The command also returns TCL OK regardless of any errors encountered during execution.

**NOTE:** Any errors encountered on the command-line, while launching the command, will be returned. Only errors occurring inside the command will be trapped.

-verbose - (Optional) Temporarily override any message limits and return all messages from this command.

**NOTE:** Message limits can be defined with the set msg config command.

<condition\_expression> - (Required) Specify an expression for the condition. If the

condition evaluates to true, the simulation will run the specified <commands> . Specific

operators that can be used in condition expressions are "equal" (==), and "not-equal" (!=).

Numeric comparison operators <, >, <=, and >= can also be used. Multiple filter expressions

can be joined by AND and OR (&& and ||).

<commands> - (Required) Specify the Tcl commands or Tcl procedure to run when the

<condition\_expression> is true. This command is surrounded by {} (braces). The

command can include standard Tcl commands and simulation Tcl commands, except run,

restart, and step. Tcl variables used in the condition expression are surrounded by quotes

"" instead of {} so variable substitution can be performed. Refer to the Vivado Design Suite User

Guide: Using Tcl Scripting (UG894) for more information on variable substitution.

### **Examples**

The following example defines a condition named resetLow, that becomes true when the reset signal is low, and then puts a message to the standard output, and stops the current simulation:

```

add_condition -name resetLow {/testbench/reset == 0 } {

puts "Condition Reset was encountered at [current_time]. Stopping simulation."

stop }

```

This next example defines a Tcl procedure, called myProc, that uses the add\_force command to define clk and reset signal values, and print a standard message when it completes. A condition is then added that calls myProc when reset is low:

```

proc myProc {} {

add_force clk {0 1} { 1 2} -repeat_every 4 -cancel_after 500

add_force reset 1

run 10 ns

remove_force force2

puts "Reached end of myProc"

}

add condition -radix unsigned /top/reset==0 myproc

```

- add\_force

- stop

# add\_drc\_checks

Add DRC rule check objects to a rule deck.

### **Syntax**

```

add_drc_checks [-of_objects <args>] [-regexp] [-nocase] [-filter <arg>]

-ruledeck <arg> [-quiet] [-verbose] [<patterns>]

```

#### **Returns**

Drc\_check

### **Usage**

| Name                     | Description                                                            |

|--------------------------|------------------------------------------------------------------------|

| [-of_objects]            | Get 'rule_check' objects of these types: 'drc_ruledeck'.               |

| [-regexp]                | Patterns are full regular expressions                                  |

| [-nocase]                | Perform case-insensitive matching. (valid only when -regexp specified) |

| [-filter]                | Filter list with expression                                            |

| -ruledeck                | DRC rule deck to modify                                                |

| [-quiet]                 | Ignore command errors                                                  |

| [-verbose]               | Suspend message limits during command execution                        |

| [ <patterns>]</patterns> | Match the 'rule_check' objects against patterns. Default: *            |

### **Categories**

DRC, Object

### **Description**

Add design rule checks to the specified drc\_ruledeck object.

A rule deck is a collection of design rule checks grouped for convenience, to be run with the report\_drc command at different stages of the Xilinx design flow, such as during I/O planning or placement. The tool comes with a set of factory defined rule decks, but you can also create new user-defined rule decks with the create\_drc\_ruledeck command.

Use the  $get\_drc\_ruledecks$  command to return a list of the currently defined rule decks available for use in the  $report\_drc$  command.

You can add standard factory defined rule checks to the rule deck, or add user-defined rule checks that were created using the <code>create\_drc\_check</code> command. Use the <code>get\_drc\_checks</code> command to get a list of checks that can be added to a rule deck.

Checks can also be removed from a rule deck using the remove drc checks command.

**NOTE:** To temporarily disable a specific DRC rule, use the <code>set\_property</code> command to set the <code>IS\_ENABLED</code> property for the rule to false. This will disable the rule from being run in <code>report\_drc</code>, without having to remove the rule from the rule deck. Use <code>reset\_drc\_check</code> to restore the rule to its default setting.

This command returns the list of design rule checks that were added to the rule deck.

### **Arguments**

-of\_objects <arg> - (Optional) Add the rule checks of the specified drc\_ruledeck object to the specified rule deck. This has the effect of copying the rules from one rule deck into another.

**NOTE:** The -of\_objects option requires objects to be specified using the get\_\* commands, such as get\_cells or get\_pins, rather than specifying objects by name. In addition, -of objects cannot be used with a search pattern.

-regexp - (Optional) Specifies that the search patterns are written as regular expressions. Both search patterns and -filter expressions must be written as regular expressions when this argument is used. Xilinx regular expression Tcl commands are always anchored to the start of the search string. You can add ".\*" to the beginning or end of a search string to widen the search to include a substring. See http://perldoc.perl.org/perlre.html for help with regular expression syntax.

**NOTE:** The Tcl built-in command regexp is not anchored, and works as a standard Tcl command. For more information refer to http://www.tcl.tk/man/tcl8.5/TclCmd/regexp.htm.

-nocase - (Optional) Perform case-insensitive matching when a pattern has been specified. This argument applies to the use of -regexp only.

-filter <args> - (Optional) Filter the results list with the specified expression. The -filter argument filters the list of objects returned by the search pattern, based on specified property values. You can find the properties on an object with the report\_property or list property commands.

The filter search pattern should be quoted to avoid having to escape special characters that may be found in net, pin, or cell names, or other properties. String matching is case-sensitive and is always anchored to the start and to the end of the search string. The wildcard "\*" character can be used at the beginning or at the end of a search string to widen the search to include a substring of the property value.

**NOTE:** The filter returns an object if a specified property exists on the object, and the specified pattern matches the property value on the object. In the case of the "\*" wildcard character, this will match a property with a defined value of "".

For string comparison, the specific operators that can be used in filter expressions are "equal" (==), "not-equal" (!=), "match" (= $\sim$ ), and "not-match" (! $\sim$ ). Numeric comparison operators <, >, <=, and >= can also be used. Multiple filter expressions can be joined by AND and OR (&& and ||). The following gets input pins that do NOT contain the "RESET" substring within their name:

```

get pins * -filter {DIRECTION == IN && NAME !~ "*RESET*"}

```

Boolean (bool) type properties can be directly evaluated in filter expressions as true or not true:

```

-filter {IS PRIMITIVE && !IS LOC FIXED}

```

-ruledeck <arg> - (Required) The name of the rule deck to add the specified design rule checks to.

-quiet - (Optional) Execute the command quietly, returning no messages from the command. The command also returns TCL\_OK regardless of any errors encountered during execution.

**NOTE:** Any errors encountered on the command-line, while launching the command, will be returned. Only errors occurring inside the command will be trapped.

-verbose - (Optional) Temporarily override any message limits and return all messages from this command.

**NOTE:** Message limits can be defined with the set\_msg\_config command.